# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

Spécialité : **Informatique** École doctorale Informatique, Télécommunications et Électronique (Paris)

Présentée par **Jean-Yves VET** pour obtenir le grade de

#### DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

#### Parallélisme de tâches et localité de données dans un contexte multi-modèle de programmation pour supercalculateurs hiérarchiques et hétérogènes

Organisme d'accueil CEA, DAM, DIF F-91297 Arpajon, France

#### Après avis de :

| M. François Bodin | Professeur des Universités | Rapporteur |

|-------------------|----------------------------|------------|

| M. Raymond NAMYST | Professeur des Universités | Rapporteur |

#### Soutenue le 25 novembre 2013 devant la commission d'examen composée de :

| M. François Bodin       | Professeur des Universités              | Rapporteur           |  |

|-------------------------|-----------------------------------------|----------------------|--|

| M. Patrick CARRIBAULT   | Ingénieur-chercheur au CEA              | <b>Encadrant CEA</b> |  |

| M. Albert Сонен         | Directeur de recherche à l'INRIA        | Directeur de thèse   |  |

| M. Thierry GAUTIER      | Chercheur à l'INRIA                     | Examinateur          |  |

| M. Raymond NAMYST       | Professeur des Universités              | Rapporteur           |  |

| M. Jean-Pierre PANZIERA | Directeur de l'ingénierie HPC chez BULL | Examinateur          |  |

| M. Gaël Thomas          | Maître de Conférences                   | Président            |  |

#### Remerciements

On ne peut jamais tourner une page de sa vie sans que s'y accroche une certaine nostalgie a écrit Ève Belisle. Au terme de cette grande aventure que peut être le parcours sinueux d'une thèse, je souhaite remercier toutes celles et tous ceux qui m'ont permis de découvrir le monde de la recherche, de progresser dans cette voie et de rendre cette période la plus plaisante possible. Je suis persuadé que je serai vite rattrapé par ce sentiment de nostalgie que j'associerai à cette époque de ma vie, très riche en apprentissages et en rencontres formidables.

Je tiens tout d'abord à témoigner ma gratitude à M. François Bodin et M. Raymond Namyst, pour avoir bien voulu juger mes travaux en tant que rapporteurs et qu'examinateurs. Merci également à M. Thierry Gautier, M. Jean-Pierre Panziera et M. Gaël Thomas pour avoir accepté de se joindre au jury de ma thèse.

Ma reconnaissance va à Albert Cohen. Il fut un directeur de thèse précieux, doué de capacités de raisonnement et de travail qui m'ont fortement impressionné et durablement marqué. Merci à toi Albert pour ton aménité, ta patience maintes fois éprouvée et ton soutien sans faille durant ces trois années. Je remercie chaleureusement Patrick Carribault qui a accepté de prendre en charge la responsabilité de mon encadrement au CEA. Patrick, tu as été un encadrant à l'écoute et qui a su faire preuve d'une grande pédagogie à mon égard. Tel un maître d'armes tu as su attirer mon attention sur la nécessité de prendre régulièrement du recul pour mieux faire mouche (et éviter de recourir à des outils *redondants*). Je suis navré de t'avoir fait subir, à répétition, mon humour noir et mon caractère peu optimiste en apparence. Je suis néanmoins ravi d'avoir pu récupérer la location de ton ancien logement (m'épargnant ainsi d'avoir à affronter les terribles ragondins d'Arpajon).

Amical clin d'œil à tous les membres de l'équipe MPC. J'ai grandement apprécié votre sympathie, votre soutien et votre partage de savoir-faire. En particulier, merci à Marc pour avoir passé, à l'époque, le flambeau à Patrick afin qu'il récupère le logement qu'il m'a laissé par la suite. Peut-être, la légende voudrat-elle un jour que cette histoire tire ses origines d'une tradition plus ancienne. Ainsi, dois-je comprendre que je suis désormais investi d'une mission quasi ancestrale : ce logement restera au sein de l'équipe MPC! Merci à Jean-Baptiste, collègue de bureau, co-renifleur en blouse blanche et amplificateur de folie (je t'avais prévenu que nous finirions en HP). Merci à Jérôme d'avoir su trouver le courage nécessaire pour nous supporter dans notre bureau exigüe, ne fut-ce que pour quelques mois ; pardon de t'avoir communiqué notre démence (écureuil!). Merci à Sylvain d'avoir été toujours si avenant et disponible, à Emmanuelle pour nous avoir communiqué à tous ta bonne humeur habituelle (et tes excellentes adresses de restaurants), à Antoine pour avoir tenté à maintes reprises de me motiver à courir. Merci à François pour tes interventions efficaces sur les machines, à Camille aka DJ Vector paddé, à Augustin, à Julien, à Aurèle dont le patronyme me fera toujours penser à un boys band moldave auteurs de paroles très appropriées (NUMA NUMA). Merci à Sébastien, maître Yoda des allocations mémoires, pour ses conseils techniques et pour nos discussions passionnantes. J'espère que tu continueras à m'épauler dans la même palanquée pour quelques bulles en tant que parfait binôme de plongée sous-marine. Pourrions-nous enfin trancher si le père d'Ondine a finalement bien pris la barque à congres au lieu de la barque à bars sachant que le congre est barivore?

En évoquant ce questionnement de barque qui nous tourmente tant, un grand merci à mon parfait associé Mickaël pour avoir dirigé la nôtre de barque, seul à la barre pendant cette longue période. Tu m'as laissé l'opportunité de réaliser cette thèse sereinement et grâce à toi, nôtre entreprise ressemble désormais à un véritable petit navire.

Merci à tous les autres collègues que j'ai pu rencontrer à l'INRIA, à l'ENS ou au CEA, pour nos échanges enrichissants. Mes pensées vont tout particulièrement à Feng, Michael, Riyadh, Sébastien, Jordan *le philosophe des caches*, Betrand, Manu, Nicolas, Alex *Flash Gordon*, Thomas, Xavier.

Merci Lucie, pour avoir enduré mes variations d'humeur pendant mes périodes de stress et de nuits blanches. Tu as su m'apporter l'écoute, la tendresse et le réconfort dont j'avais besoin pour avancer et surmonter l'épreuve de la rédaction.

Enfin, mes plus profonds remerciements vont à mes parents qui sont extraordinaires. Merci pour votre soutien inconditionnel pendant toutes ces années. Malgré la distance, vous avez été à mes côtés à chaque instant pour me donner confiance en moi. C'est grâce à cette présence et vos encouragements que j'ai pu saisir la chance d'approfondir mes études dans un domaine qui me passionne et cela dans les meilleures conditions que l'on puisse souhaiter. Merci.

#### Résumé

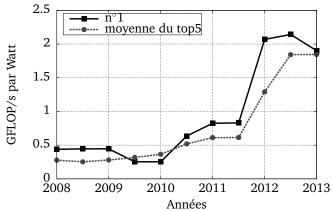

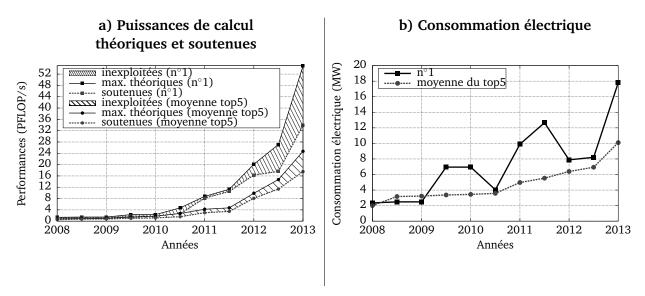

Des besoins toujours plus conséquents en puissance de calcul, notamment pour faire face à de nouveaux défis dans le domaine de la simulation numérique, ont entraîné la complexification des movens de traitement. Nous avons étudié des nœuds de calcul issus de supercalculateurs de classe pétaflopique tels que Tera-100 détenu par le CEA ainsi que la machine Curie appartenant à GENCI. Au cours de l'histoire des supercalculateurs, les architectures matérielles ont capitalisé de nombreuses innovations technologiques dont certaines ont permis de contourner des obstacles qui auraient pu considérablement retarder la progression des capacités de calcul. La consommation électrique est désormais devenue le principal frein à la conception de nouvelles machines plus performantes. Afin de progresser dans cette quête de puissance de traitement, des grappes de calcul intégrant des processeurs de différentes natures ont vu le jour. Ces machines hétérogènes combinent les capacités d'exécution de processeurs traditionnels à celles de composants spécialisés appelés accélérateurs. Ceux-ci présentent de meilleures caractéristiques de calcul pour des opérations massivement parallèles. En particulier, ces composants spécifiques offrent un rapport performance/consommation réduit du fait de l'adjonction de multiples unités d'exécution matériellement simplifiées. Avec la multiplication du nombre d'unités de calcul se pose la question de l'efficacité d'exploitation de ces machines sophistiquées. Les programmeurs d'applications sont dès à présent contraints de coordonner toutes ces ressources de calcul hétérogènes, lesquelles peuvent recourir à des modèles de programmation distincts pour mieux exprimer le degré de parallélisme d'une application. ce qui en intensifie la complexité du fait de leur exploitation conjointe. Toutes ces unités de traitement sont amenées à échanger des résultats de calcul intermédiaires pour produire, in fine, une solution correcte. Pourtant, certaines mémoires déportées dans les accélérateurs n'étant pas maintenues matériellement cohérentes entre elles et avec la mémoire centrale, cela impose aux développeurs de gérer eux-mêmes les transferts de données aux moments les plus appropriés, et introduit par conséquent une difficulté de programmation supplémentaire. Par ailleurs, les performances des programmes sont fortement conditionnées par la facon dont toutes les ressources de calcul accèdent aux données. Pour répondre à une problématique de pression accrue sur la mémoire centrale et pour être en mesure de maximiser le degré d'occupation des unités de traitement, les machines s'articulent autour d'une imbrication de plus en plus marquée de diverses mémoires. Favoriser une utilisation performante de la hiérarchie des mémoires passe par des schémas d'accès spécifiques qui respectent des principes de localité des données. Ces contraintes d'accès permettent de tirer un meilleur parti des machines tout en limitant les dépenses énergétiques induites par des accès distants, mais rendent en contrepartie l'élaboration des programmes plus délicate. Ainsi, il s'agit dès lors d'exploiter simultanément des architectures hétérogènes et hiérarchiques dans un contexte de grappes de calcul, tout en portant un intérêt particulier à l'accès aux données.

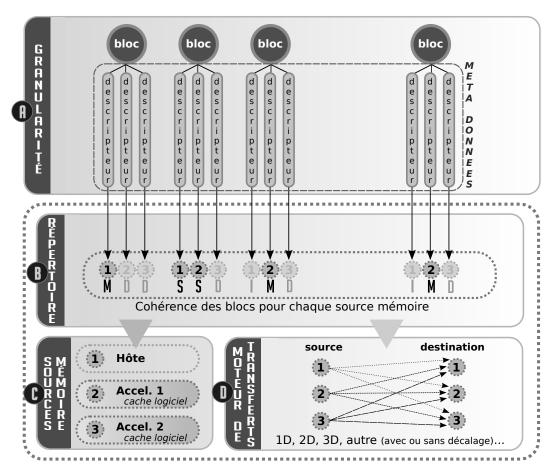

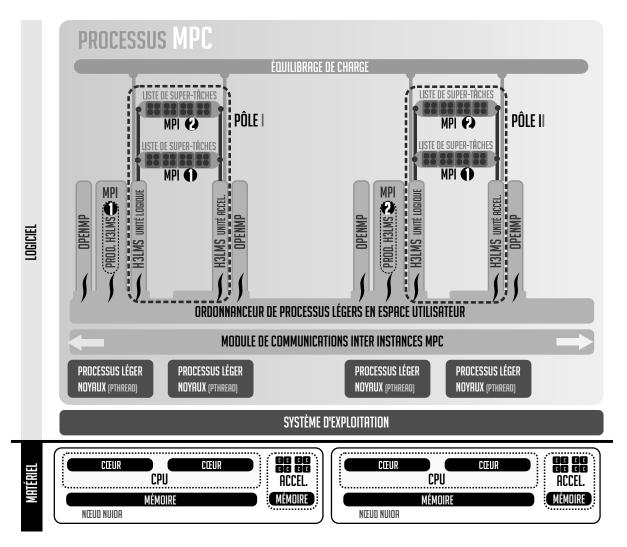

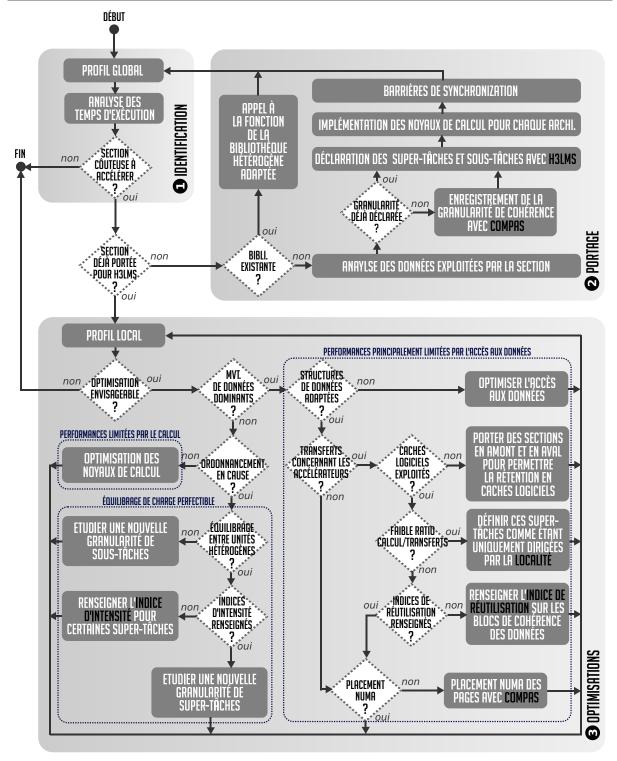

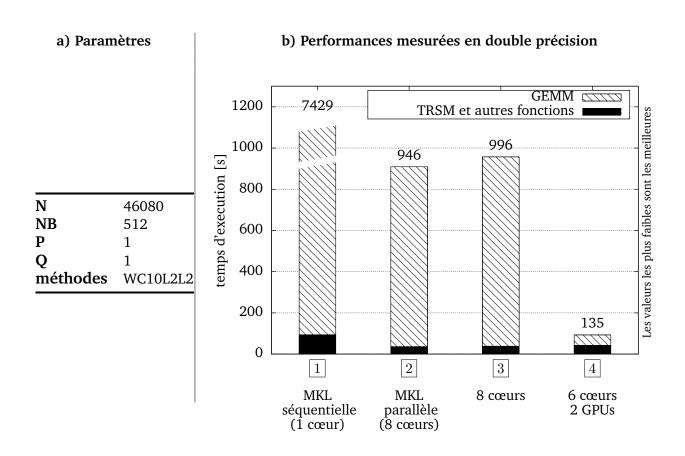

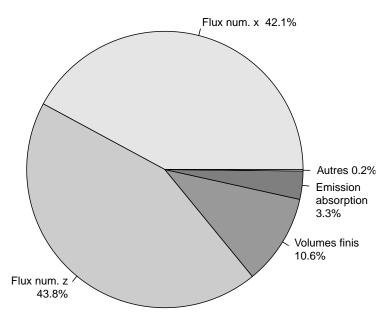

Cette thèse présente des contributions permettant d'accentuer la localité des données dans des nœuds de calcul hétérogènes. Elles s'appuient sur un modèle de programmation par tâches, dont l'originalité réside dans l'ajustement de la quantité de calcul en fonction de l'unité d'exécution ciblée. Ce modèle de programmation est particulièrement adapté à un équilibrage de charge dynamique entre des ressources de calcul hétérogènes. Il favorise une meilleure exploitation des unités de traitement en offrant une meilleure réactivité en présence de variations des temps d'exécution, lesquelles peuvent être générées par des codes de calcul irréguliers ou des mécanismes matériels difficilement prévisibles. De plus, grâce à une sémantique adaptée, la déclaration des tâches de calcul facilite le recours à des mécanismes de gestion automatisée des opérations de cohérence des mémoires déportées et décharge les développeurs de cette tâche fastidieuse et source d'erreurs. Nous avons développé la plateforme d'exécution H3LMS afin d' agréger les propositions de cette thèse. Cette plateforme est intégrée à l'environnement de programmation MPC, développé conjointement par le CEA et le laboratoire Exascale Computing Research afin de faciliter la cohabitation de plusieurs modèles de programmation pour une meilleure exploitation des grappes de calcul. H3LMS permet, entre autres, de mieux aiguiller les tâches vers les unités de traitement appropriées en réduisant la quantité de coûteux accès distants au sein d'un nœud de calcul. Ces travaux s'intéressent également à l'adaptation de codes de simulation existants, conçus à l'origine pour exploiter exclusivement des processeurs traditionnels et pouvant comporter plusieurs dizaines voire plusieurs centaines de milliers de lignes de code. En particulier, des applications transparentes à des codes de simulation existants sont présentées à travers l'instrumentation de bibliothèques standards telles que les BLAS. Les performances de la solution développée sont évaluées sur la bibliothèque Linpack et par une application numérique réaliste du CEA.

### Introduction

"Si six scies scient six cyprès, combien de cyprès scient six cent six scies?"

Anonyme, virelangue français

Les capacités de calcul de la machine d'IBM *Deep Blue* [1] marquèrent les esprits en 1997, puisqu'elles permirent de battre officiellement le champion du monde d'échecs *Gary Kasparov*, considéré comme l'un des meilleurs joueurs de l'histoire. Plus récemment, près de deux cent mille milliards de composants électroniques élémentaires<sup>1</sup>, appelés *transistors*, ont été agrégés pour fournir à *Titan*<sup>2</sup> la capacité de calcul qui l'a élevée, en novembre 2012, au rang de machine la plus puissante au monde. À titre de comparaison, cela correspondrait à la quantité de neurones totalisée par près de deux-mille cerveaux humains. Ce nombre colossal n'est qu'un arrêt sur image dans l'histoire des superordinateurs et va vraisemblablement continuer à s'élever de manière exponentielle avec les prochaines générations de machine. En effet, la loi de Gordon E. Moore [3], réévaluée en 1975, n'a jamais failli en prédisant un doublement de la densité des puces électroniques tous les deux ans.

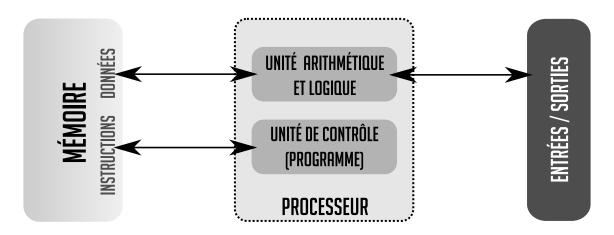

L'époque des premiers calculateurs semble bien lointaine lorsque nous comparons leurs performances à celles de nos machines contemporaines. En 2013, elles disposaient d'une capacité de calcul d'un million de milliards de fois plus conséquente<sup>3</sup>. Leur évolution a en réalité progressé à une vitesse effrénée. La préhistoire de ces machines remonte à 1642 lorsque Blaise Pascal inventa la machine arithmétique surnommée la Pascaline [4], première machine à calculer purement mécanique. En 1834, le précurseur britannique Charles Babbage imagina la machine analytique [5]. Bien que jamais construite, elle ouvrit la voie aux machines programmables en étant dotée, sur le papier, de mémoires, d'imprimantes, d'une unité centrale et de lecteurs de cartes inspirés du métier à tisser Jacquard pour y insérer les instructions et les données sur lesquelles elles opèrent. Puis, en moins d'un siècle, les avancées ont permis de passer des grandes théories, telle celle exposée dans l'article fondateur de la science informatique par Alan Turing en 1936 [6], à l'automatisation concrète du calcul par de puissantes machines. Peu avant la Seconde Guerre mondiale, les premiers calculateurs électromécaniques sont apparus selon l'idée de Turing. Quelques années plus tard, en 1941, le calculateur Z3 est achevé et est alors considéré comme la première machine programmable fonctionnelle. Ce système, conçu par Konrad Zuse, fut employé par la Wehrmacht pour le guidage de missiles. La série-Z [7] inaugura bon nombres d'avancées technologiques telle celle de l'arithmétique binaire et celle des nombres à virgule flottante en tant qu'approximations de nombres réels [8]. Après la Seconde Guerre mondiale, ces calculateurs ont évolué et ont donné naissance à des machines au fonctionnement purement électronique que nous appelons depuis des *ordinateurs*. Initiées par la découverte du transistor en 1947, les performances de ces machines électroniques ont été considérablement décuplées par la suite.

$<sup>^118\,688</sup>$  AMD Opteron 6274 de 2,4  $\times$   $10^9$  transistors et 18 688 Nvidia Tesla K20X de 7,1  $\times$   $10^9$  transistors.

<sup>&</sup>lt;sup>2</sup>Classement TOP500, novembre 2012 [2].

$<sup>^{3}</sup>$ *Titan* (2012) : 17 PFLOP/s || *Z3* (1941) : 20 FLOP/s.

Ces ordinateurs ont été rapidement employés pour reproduire, par le calcul, des phénomènes physiques. Ces *simulations informatiques* ont ainsi permis de décrire des phénomènes sans qu'ils ne se soient réellement produits. La première simulation a été élaborée lors de la Seconde Guerre mondiale pour répondre aux besoins de conception et de modélisation du *projet Manhattan*<sup>4</sup>, porté notamment par le mathématicien et physicien américain d'origine hongroise John von Neumann [9]. En 1953 eu lieu la première simulation dans le domaine civil en physique théorique, connue sous le nom d'*expérience de Fermi-Pasta-Ulam* [10]. Depuis, les simulations numériques se sont répandues dans divers domaines. Elles permettent, par exemple, d'anticiper des phénomènes météorologiques ou sont encore employées en tant qu'atout financier dans l'industrie en accélérant des cycles de conception. Certains secteurs nécessitent une capacité de traitement de plus en plus conséquente pour simuler des systèmes toujours plus complexes, donnant lieu à une course perpétuelle à la puissance de calcul.

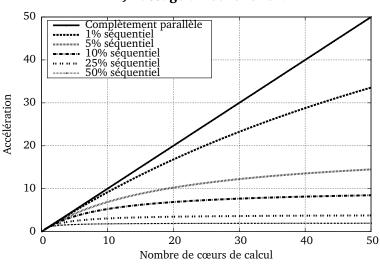

Le terme de supercalculateur (ou superordinateur) apparaît dans les années soixante. Il s'agit d'un ordinateur conçu pour atteindre les plus hautes performances de calcul possibles avec les technologies connues lors de sa conception. La science des supercalculateurs est appelée calcul haute performance (HPC<sup>5</sup>). Les premières machines enchaînaient successivement les opérations qui étaient traitées par un unique système exécutif appelé processeur (ou CPU<sup>6</sup>). Dans les années soixante-dix, l'équivalent de la puissance de calcul de plusieurs processeurs est combinée. Afin de tirer le meilleur parti de ces machines, toutes ces unités doivent travailler de concert. C'est alors qu'a émergé le calcul parallèle permettant l'exécution simultanée de plusieurs opérations afin de les traiter plus rapidement. Ainsi, ces travaux informatiques peuvent être accélérés par rapport à des opérations successives, dites séquentielles. L'élaboration des codes calcul s'en trouve complexifiée, puisqu'il s'agit désormais de coordonner les différents processeurs qui sont amenés à échanger des résultats de calcul intermédiaires pour produire, in fine, une solution correcte. Avec la multiplication du nombre d'unités de calcul se pose la question de l'efficacité d'exploitation de ces machines sophistiquées. Une accélération linéaire n'est quasiment jamais atteinte. En d'autres termes, et en faisant écho au virelangue introductif, si des opérations sont traitées par 6 processeurs, il faudra bien souvent plus de 606 processeurs pour effectuer une quantité de calcul 101 fois plus importante pendant le même laps de temps. Optimiser l'efficacité des calculs effectués par une machine moderne est un des challenges de l'informatique parallèle.

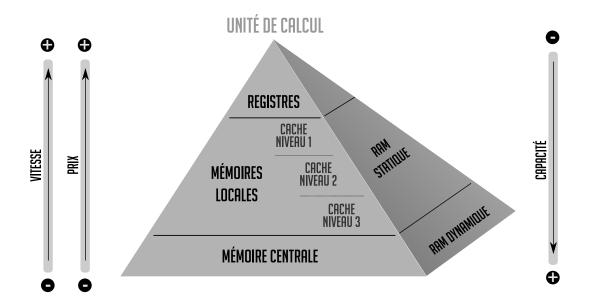

#### Contexte, objectifs et contributions

Outre un degré de parallélisme insuffisant, différents facteurs peuvent constituer un frein à l'obtention de hautes performances de calcul. L'élément certainement le plus décisif concerne l'accès aux données sur lesquelles les calculs sont réalisés. Pour les machines contemporaines, ces données sont stockées dans une imbrication de mémoires plus ou moins rapides. Lorsque les unités de traitement sont en attente de récupération de ces données, elles peuvent se trouver sous-exploitées, ce qui rallonge inutilement le temps d'exécution des programmes. Favoriser une exploitation performante de la hiérarchie des mémoires passe par des schémas d'accès spécifiques qui respectent des principes de *localité des données*. Ces contraintes d'accès permettant de tirer un meilleur parti des machines, rendent l'élaboration des programmes plus délicate. Par ailleurs, des processeurs composés de centaines, voire de milliers d'unités de traitement ont vu le jour afin de progresser dans la quête de puissance de calcul. Ceux-ci présentent de meilleures caractéristiques de calcul pour des opérations *massivement parallèles*. Ils offrent, entre autres, un rapport performance/consommation réduit du fait de l'adjonction de multiples unités de calcul simplifiées. Ils sont ainsi appelés *accélérateurs* lorsqu'ils sont combinés à des processeurs plus traditionnels. Ces

<sup>5</sup>**HPC**: High Performance Computing.

<sup>6</sup>**CPU**: Central Processing Unit.

<sup>&</sup>lt;sup>4</sup>Nom de code du projet de recherche de la première tête nucléaire.

nouvelles machines sont alors qualifiées d'hétérogènes puisqu'elles agrègent des processeurs de différentes natures et des mémoires qui peuvent être disjointes. Les programmeurs sont dès à présent contraints de coordonner ces mémoires et ces diverses ressources de calcul. Ils peuvent recourir à des modèles de programmation variés pour exprimer le degré de parallélisme le mieux adapté à chaque *microarchitecture* de processeur. Les développeurs d'applications assistent ainsi à une complexification de l'exploitation à haute performance des machines, d'une part en s'efforçant de limiter la baisse d'activité des architectures causée par la manipulation des données stockées dans la hiérarchie mémoire, et d'autre part en essayant de répartir efficacement les calculs entre toutes les ressources de traitement disponibles.

La programmation par *tâches de calcul* peut faciliter la gestion de ces machines hétérogènes. Elle organise les instructions par lots de traitements appelés *tâches* et participe à renforcer les principes de localité de données. Ce modèle repose sur un logiciel appelé *plate-forme d'exécution* qui répartit dynamiquement, entre les différentes ressources de traitement, les tâches décrites dans un code de calcul. Les opérations embarquées dans une tâche peuvent être exprimées à l'aide d'un ou de plusieurs autres modèles afin d'offrir une compatibilité avec les différents processeurs qui peuvent être ciblés. La programmation par tâches de calcul permet aussi d'établir des mécanismes capables de décharger le programmeur de certaines contraintes d'exploitation liées à la gestion de la mémoire. L'objectif de cette thèse est l'élaboration d'une telle plate-forme permettant de recourir dynamiquement à des ressources de calcul hétérogènes, tout en portant un intérêt particulier à l'accès aux données pour atteindre de hautes performances. Ces travaux s'intéressent également au portage progressif de codes de simulation existants, conçus à l'origine pour des processeurs traditionnels. Les contributions suivantes sont ainsi proposées :

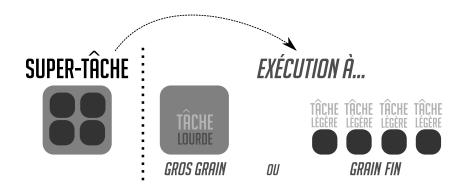

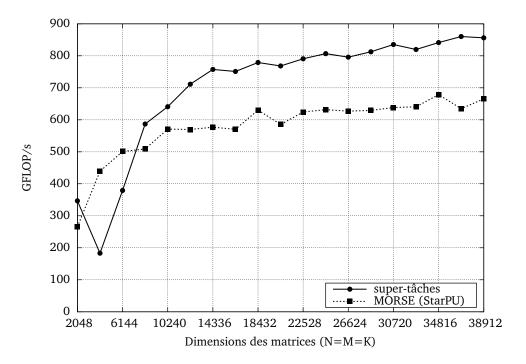

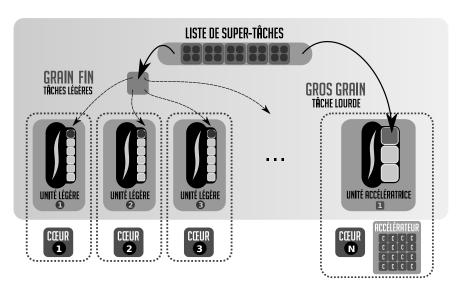

- 1. Des tâches de calcul décomposables permettant d'adapter dynamiquement la charge de travail en fonction des unités de calcul ciblées tout en amplifiant la localité spatiale des données (chapitre 4).

- 2. Une **coopération hiérarchique** des unités exécutantes en s'appuyant sur les contraintes architecturales des machines actuelles (chapitre 4).

- 3. Une interface de programmation permettant de **répartir des données** en mémoire centrale afin de réduire la quantité d'accès distants lors de l'ordonnancement des tâches de calcul (chapitre 4).

- 4. Une **gestion automatisée** des données en prenant en charge leur transfert entre les différentes mémoires et en assurant leur cohérence (chapitre 5).

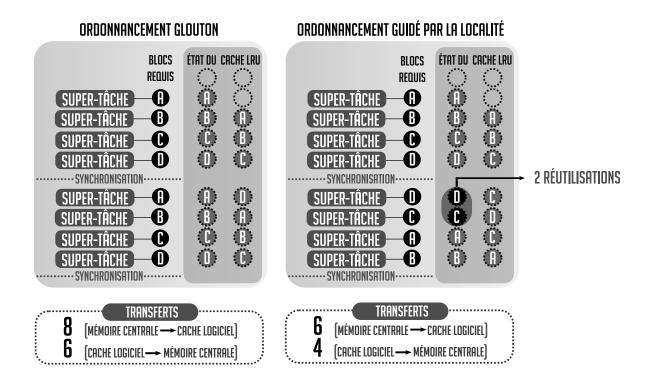

- 5. Une **rétention accrue des données** dans les mémoires déportées, couplée à l'ordonnancement des opérations afin de diminuer la quantité des données véhiculées (chapitre 5).

- 6. Une proposition d'interface permettant la **réutilisation de données préchargées** entre des appels à une bibliothèque de calculs optimisés et d'autres traitements (chapitre 5).

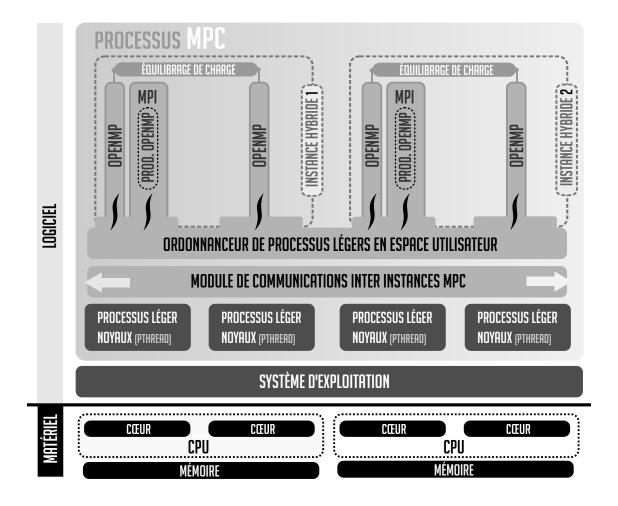

- 7. La **conception d'un support d'exécution** agrégeant les fonctionnalités précédentes et intégré à un environnement de programmation facilitant les interactions avec d'autres modèles de programmation (chapitre 6).

Certaines des ces contributions ont été publiées et présentées à MUTIPROG<sup>7</sup> 2012 [11].

<sup>&</sup>lt;sup>7</sup>**MULTIPROG**: Programmability Issues for Heterogeneous Multicores.

De manière générale, ce document décrit le couplage entre l'ordonnancement de tâches de calcul à granularités multiples avec des politiques de remplacement de caches logiciels, tout en amplifiant la localité spatiale des données. En particulier, cette solution est évaluée sur une application numérique réaliste dont les performances sont limitées par la bande passante mémoire. Grâce aux contributions qui seront détaillées tout au long du manuscrit, la plate-forme H3LMS que nous avons développée permet d'accélérer cette application d'un facteur  $2,64\times$  en exploitant deux processeurs graphiques et deux processeurs centraux par rapport à une exécution parallèle reposant uniquement sur les cœurs de calcul généralistes.

#### Organisation du document

Ce manuscrit est organisé en trois parties. La première précise le contexte. Elle met en exergue, dans un premier chapitre, les besoins en puissance de calcul des codes de simulation tout en retraçant l'évolution des architectures matérielles. Les avancées technologiques y sont introduites en insistant sur les aspects limitant induits par l'accès aux données. Le chapitre 2 explore plus en détails les différentes contraintes associées à la récupération des données dans les mémoires d'une machine parallèle moderne. Le chapitre 3 dépeint ensuite les modèles de programmation à disposition des développeurs de codes de simulation ainsi que l'état de l'art en matière d'équilibrage de charge dynamique et hétérogène.

La deuxième partie détaille les contributions en évaluant au fur et à mesure ces propositions sur des codes de calcul d'algèbre linéaire. Le chapitre 4 décrit les travaux associés à un renforcement de la localité spatiale grâce à une décomposition à la volée des tâches de calcul, à une organisation hiérarchique de leur exécution et à un placement initial soigneusement étudié des données en mémoire. Le chapitre 5 expose les travaux entrepris pour automatiser la gestion de mémoires disjointes et amplifier la localité temporelle grâce à des mécanismes de rétention de données. Le chapitre 6 présente les mécanismes d'ordonnancement permettant d'agréger les contributions sur la localité des données dans une unique plate-forme d'exécution. Cette dernière est intégrée à un environnement facilitant une cohabitation avec d'autres modèles de programmation. Le chapitre 7 évalue les performances de cette solution en exposant les résultats obtenus à partir de la bibliothèque de performance *Linpack* et d'une mini application du CEA.

Enfin, une troisième et dernière partie synthétise les travaux accomplis, puis aborde les améliorations et les perspectives envisagées à court et à plus long termes.

# Table des matières

| In | trodu | action                                                              | 7  |

|----|-------|---------------------------------------------------------------------|----|

| Ι  | Con   | ntexte                                                              | 15 |

| 1  | Les   | supercalculateurs au service des codes de simulation                | 17 |

|    | 1.1   | La puissance de calcul pour la simulation numérique                 | 19 |

|    |       | Les architectures parallèles et l'évolution des supercalculateurs   | 20 |

|    |       | 1.2.1 Des machines séquentielles aux grappes de calcul              | 20 |

|    |       | 1.2.2 La révolution des processeurs multi-cœurs                     | 21 |

|    |       | 1.2.3 Les accélérateurs massivement parallèles                      | 23 |

|    | 1.3   | Les supercalculateurs contemporains                                 | 27 |

|    |       | 1.3.1 L'émergence des grappes de calcul hétérogènes                 |    |

|    | 1.4   | Les supercalculateurs de prochaine génération                       |    |

|    |       | 1.4.1 Piste des architectures hétérogènes                           |    |

|    |       | 1.4.2 Piste des architectures homogènes                             |    |

|    | 1.5   | Lien entre la puissance de calcul et la consommation électrique     |    |

|    |       | 1.5.1 Similitudes avec le domaine de l'embarqué                     |    |

|    |       | 1.5.2 Puissance de calcul effective                                 | 31 |

| 2  | Les   | performances assujetties au chargement des données                  | 33 |

|    |       | L'organisation hiérarchique de la mémoire                           |    |

|    |       | Imbrication et cohérence des mémoires locales                       |    |

|    |       | 2.2.1 Mémoires caches dédiées à un cœur de calcul                   |    |

|    |       | 2.2.2 La cohérence des données dans les mémoires caches             | 38 |

|    |       | 2.2.3 Mémoires caches partagées entre plusieurs cœurs de calcul     | 40 |

|    | 2.3   | Les accès à la mémoire centrale par les processeurs                 | 41 |

|    |       | 2.3.1 Des accès non uniformes à la mémoire centrale                 | 42 |

|    |       | 2.3.2 Bande passante limitée par cœur de calcul                     | 46 |

|    | 2.4   | Les accès à la mémoire centrale par les accélérateurs matériels     | 46 |

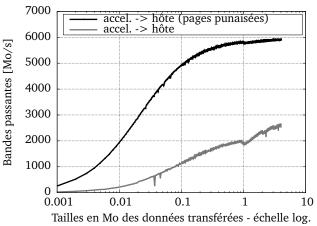

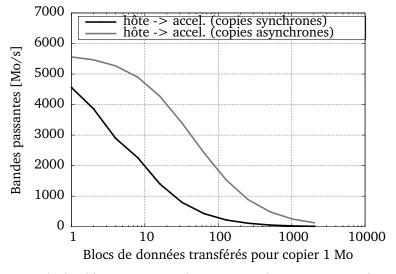

|    |       | 2.4.1 Les contraintes d'accès à la mémoire centrale en mode DMA     | 48 |

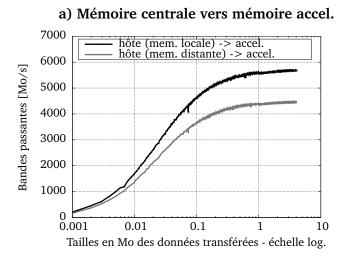

|    |       | 2.4.2 Des accès asymétriques et non-uniformes à la mémoire centrale | 49 |

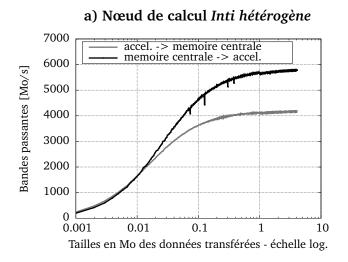

|    |       | 2.4.3 L'exploitation des mémoires embarquées                        | 51 |

| 3  | Les   | modèles de programmation parallèles                                 | 55 |

|    | 3.1   | Des codes séquentiels aux codes parallèles                          | 57 |

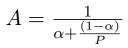

|    |       | 3.1.1 Impact d'une portion séquentielle dans un code parallèle      | 58 |

|    | 3.2   | Les modèles de programmation parallèles statiques                   | 59 |

|    |       | 3.2.1 Les processus légers                                          | 60 |

|    |       | 3.2.2 Le passage de messages                                        | 63 |

|    |       | 3.2.3 Les espaces d'adressage partitionnés (PGAS)                   | 62 |

|    | 3.3  | 3.2.4 Modèles pour accélérateurs                                                                                        | 64<br>64<br>66<br>69 |

|----|------|-------------------------------------------------------------------------------------------------------------------------|----------------------|

| II | Co   | ntributions                                                                                                             | 77                   |

| 4  | Loca | alités spatiales au sein des tâches hétérogènes de calcul                                                               | 79                   |

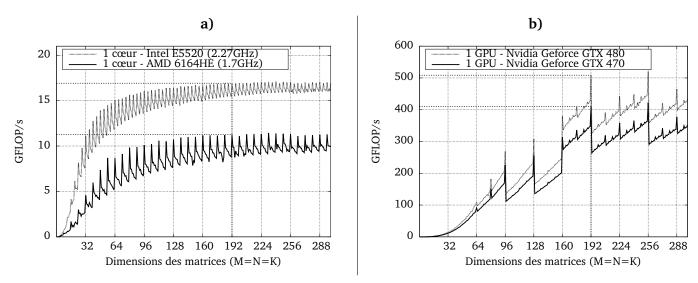

|    | 4.1  | Tâches de calcul hétérogènes à granularités multiples                                                                   | 81                   |

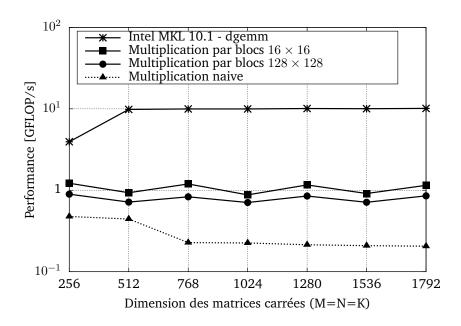

|    |      | 4.1.1 Granularité et performances disparates                                                                            | 82                   |

|    |      | 4.1.2 Tâches hétérogènes décomposables                                                                                  | 83                   |

|    |      | 4.1.3 Évaluation de la granularité variable à la demande sur LU creux par blocs                                         | 85                   |

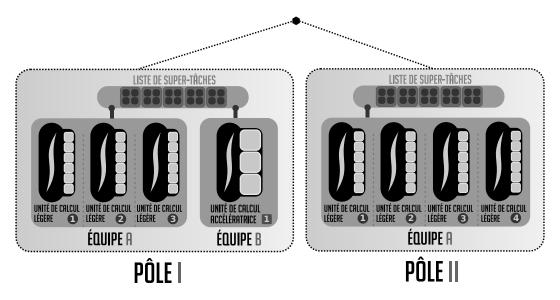

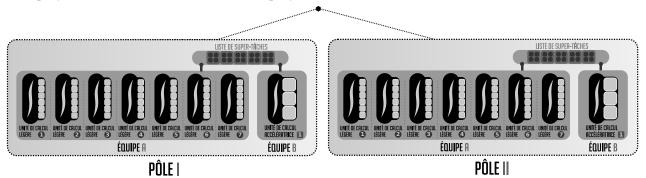

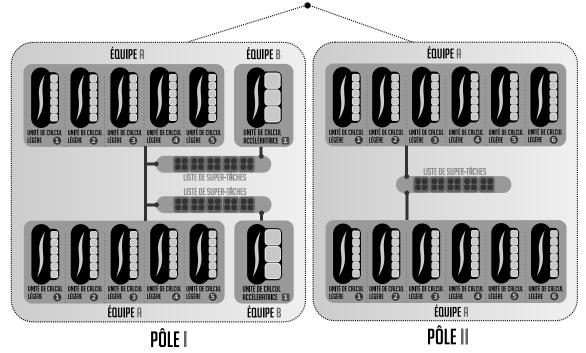

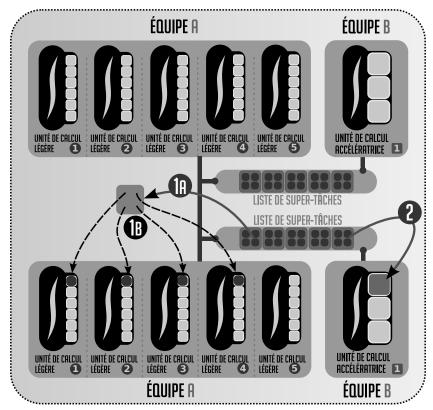

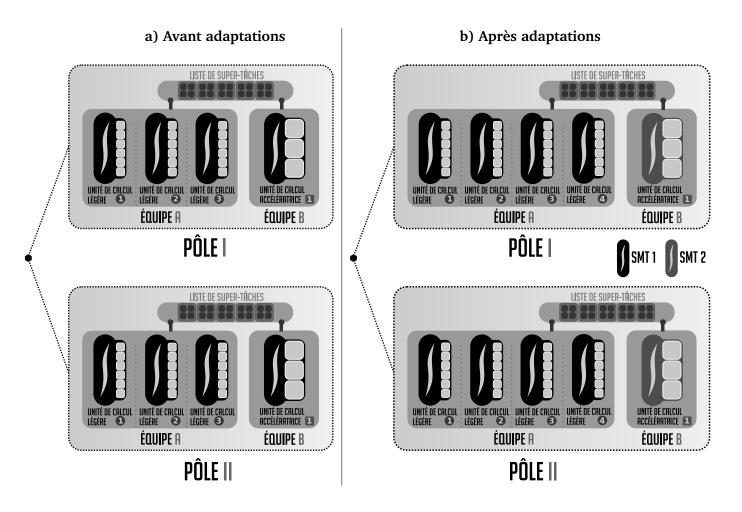

|    | 4.2  | Affinités hiérarchiques des super-tâches                                                                                | 87                   |

|    |      | 4.2.1 Organisation abstraite                                                                                            | 87                   |

|    |      | 4.2.2 Représentation en fonction de la topologie de la machine                                                          | 89                   |

|    | 4.3  | Placement initial des données                                                                                           | 90                   |

|    |      | 4.3.1 Remplacement de la fonction d'allocation                                                                          | 91                   |

|    |      | 4.3.2 Les schémas de répartition des pages mémoires                                                                     | 92                   |

|    |      | 4.3.3 Granularités                                                                                                      | 93                   |

|    |      | <ul><li>4.3.4 Les informations de localité spatiale pour aiguiller les super-tâches</li><li>4.3.5 Évaluations</li></ul> | 93<br>94             |

|    |      | 4.5.5 Evaluations                                                                                                       | 94                   |

| 5  | Gest | tion des données favorisant la localité temporelle                                                                      | 97                   |

|    | 5.1  |                                                                                                                         |                      |

|    |      | 5.1.1 Enregistrement des blocs de données                                                                               | 99                   |

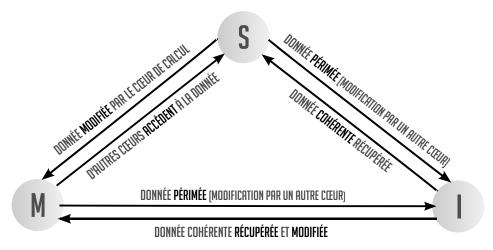

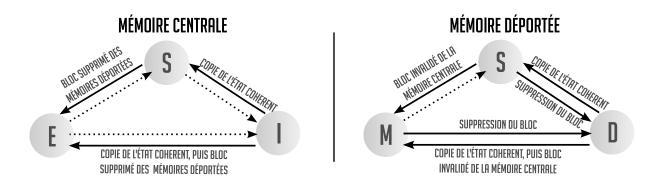

|    |      | 5.1.2 Protocole de cohérence des blocs de données                                                                       |                      |

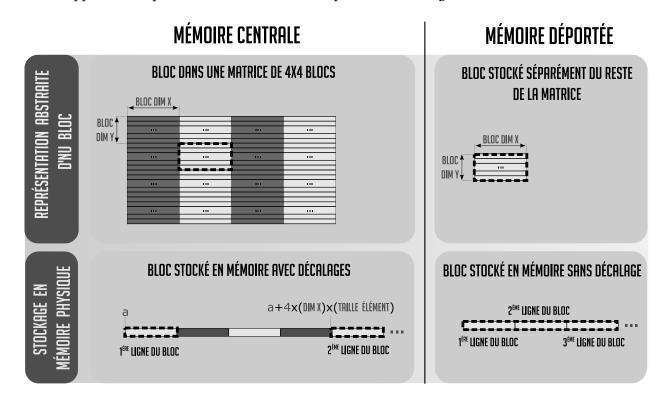

|    |      | 5.1.3 Transferts automatisés des blocs de données                                                                       | 101                  |

|    | 5.2  | Cache logiciel pour mémoire déportée                                                                                    |                      |

|    |      | 5.2.1 Interaction entre l'ordonnancement et un cache logiciel                                                           |                      |

|    |      | 5.2.2 Politique d'éviction basée sur la réutilisation des données                                                       |                      |

|    |      | 5.2.3 Affinités des tâches pour une isolation des données                                                               |                      |

|    | 5.3  | Localité temporelle entre plusieurs appels de bibliothèques                                                             |                      |

|    |      | 5.3.1 Extension de la gestion des données                                                                               |                      |

|    |      | 5.3.2 Évaluation des performances                                                                                       | 111                  |

| 6  | Ord  | onnancement gouverné par la localité des données                                                                        | 113                  |

|    | 6.1  | Interface de programmation                                                                                              |                      |

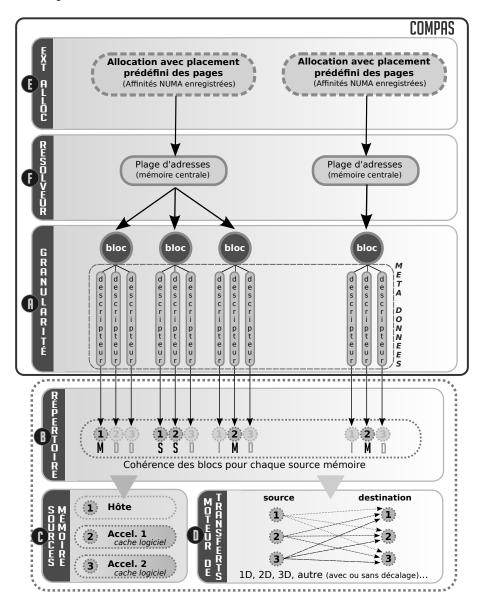

|    |      | 6.1.1 Affinités et compléments d'information sur les données (COMPAS)                                                   |                      |

|    |      | 6.1.2 Sémantiques associées aux tâches et super-tâches de calcul (H3LMS)                                                |                      |

|    | 6.2  |                                                                                                                         |                      |

|    |      | 6.2.1 Affinités standards des super-tâches                                                                              |                      |

|    |      | 6.2.2 Attribution de super-tâches spécifiques à équilibrage de charge restreint .                                       |                      |

|    | 6.3  | Équilibrage de charge dynamique hiérarchique                                                                            | 123                  |

|    |      | 6.3.1 Décomposition des super-tâches et partage de travail                                                              |                      |

|    |      | 6.3.2 Vol collaboratif hiérarchique                                                                                     |                      |

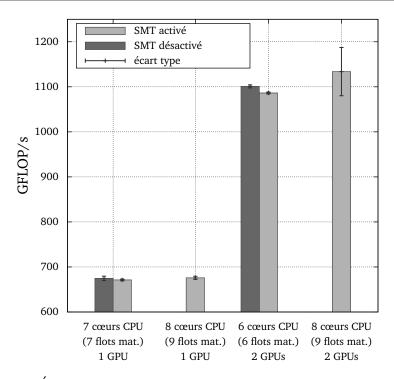

|    | 6.4  | Exploitation du SMT par l'ordonnanceur                                                                                  |                      |

|    | 6.5  | Intégration à l'environnement de développement MPC                                                                      | 127                  |

|    |      | 6.5.1 Mise en œuvre                                                                                                     | 127                  |

#### TABLE DES MATIÈRES

|     | 6.6                                             |                | Discussion                                                                        | 129<br>129<br>129 |  |  |

|-----|-------------------------------------------------|----------------|-----------------------------------------------------------------------------------|-------------------|--|--|

| 7   | <b>Évaluations</b> 7.1 High Performance Linpack |                |                                                                                   |                   |  |  |

|     | /.1                                             | 7.1.1          | Modifications                                                                     |                   |  |  |

|     |                                                 | 7.1.2          | Résultats                                                                         |                   |  |  |

|     |                                                 |                | Discussion des résultats et améliorations possibles                               |                   |  |  |

|     | 7.2                                             |                | pplication PN                                                                     |                   |  |  |

|     |                                                 | 7.2.1          | Analyse et modifications de l'algorithme                                          |                   |  |  |

|     |                                                 | 7.2.2<br>7.2.3 | Expérimentations                                                                  |                   |  |  |

|     |                                                 | 7.2.3          | Discussion des résultats et améliorations possibles                               |                   |  |  |

|     |                                                 | ,              | Possessor decreases de diniviral possessor v. | - 10              |  |  |

| III | Sy                                              | nthèse         | e et perspectives                                                                 | 147               |  |  |

| Co  | nclus                                           | sion           |                                                                                   | 149               |  |  |

|     |                                                 |                | contributions                                                                     |                   |  |  |

| Pe  | rspec                                           | tives          |                                                                                   | 151               |  |  |

|     |                                                 |                | éliorations à court terme                                                         |                   |  |  |

|     |                                                 |                | rt étendu à plusieurs types d'accélérateurs                                       |                   |  |  |

|     |                                                 |                | u portage de codes existants                                                      |                   |  |  |

|     |                                                 |                | pration des performances                                                          |                   |  |  |

|     | Réfle                                           | exion fii      | nale sur les futurs enjeux des supports d'exécution                               | 154               |  |  |

| Α   | Déta                                            | ils tecl       | nniques des nœuds de calcul                                                       | 155               |  |  |

|     |                                                 |                | IÉTĒROGÈNE                                                                        |                   |  |  |

|     |                                                 |                | 100 HÉTÉROGÈNE                                                                    |                   |  |  |

|     | A.3                                             |                | HÉTÉROGÈNE                                                                        |                   |  |  |

|     | A.4                                             |                | LARGE                                                                             |                   |  |  |

|     | A.5                                             |                | JS HÉTÉROGÈNE                                                                     |                   |  |  |

|     |                                                 |                | ERMI                                                                              |                   |  |  |

|     | 11./                                            | אוואונט        | JIVIILILIKO GLIVL                                                                 | 102               |  |  |

| Bil | oliogi                                          | aphie          |                                                                                   | 163               |  |  |

# Première partie Contexte

## Chapitre 1

# Les supercalculateurs au service des codes de simulation

"Depuis plus d'une décennie, des visionnaires ont soutenu que l'organisation d'un unique ordinateur a atteint ses limites et que des progrès significatifs ne peuvent être réalisés que par l'interconnexion d'une multitude d'ordinateurs."

Gene Amdahl, 1967

Après la Seconde Guerre mondiale, des méthodes de simulation se sont développées et ont été adoptées dans divers domaines tels que la physique, la chimie, la biologie, le génie civil, etc. Ces programmes de calcul se sont complexifiés en s'appuyant d'abord sur des représentations tridimensionnelles de plus en plus réalistes, puis après les années 90, en combinant plusieurs phénomènes physiques. Cette discipline requiert bien souvent des capacités de traitement de plus en plus importantes pour aboutir à des résultats dans un délai raisonnable et pour entreprendre des simulations plus précises et plus complètes. La conséquence de ces besoins en *calcul intensif* se traduit par une compétition effrénée pour détenir une puissance de traitement toujours plus imposante. Des supercalculateurs sont ainsi conçus en profitant des avancées technologiques pour offrir des capacités de calcul et de stockage accrues chaque année. Ils représentent un atout indéniable pour des laboratoires de recherche, pour les entreprises afin d'accélérer des cycles de conception à coûts réduits ou comme outil permettant d'asseoir la crédibilité des grandes puissances dans la conception et l'amélioration des moyens de défense et de dissuasion.

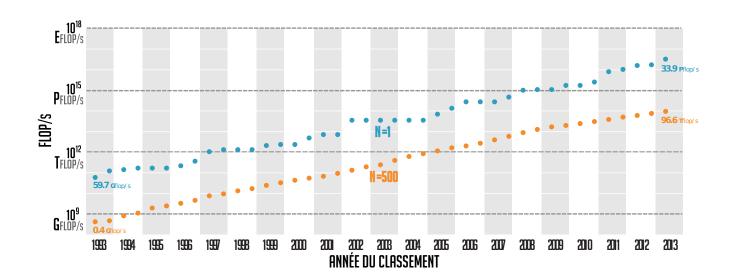

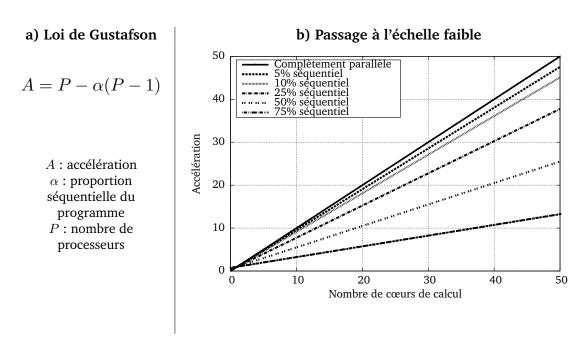

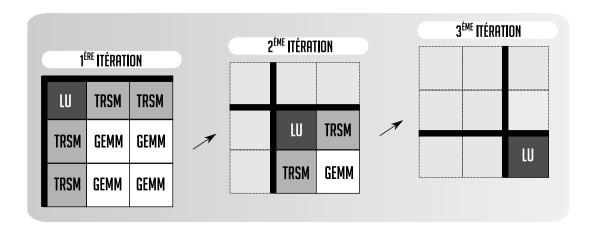

Le classement TOP500 [12] des 500 machines les plus puissantes au monde témoigne de cette course aux capacités de traitements (cf. figure 1.1). Le rang de chaque machine est établi à partir d'un test de performance<sup>8</sup> issu de la bibliothèque Linpack [13] qui résout un système de n équations à n inconnues par une factorisation de Gauss avec pivot partiel [14]. L'indice de performance est évalué en  $FLOP/s^9$  représentant la quantité moyenne d'opérations à virgules flottantes effectuées par seconde sur l'ensemble du test. Ce classement est réactualisé deux fois par an pour mieux refléter les avancées dans le domaine. Le test Linpack est un programme extrêmement optimisé. Lorsqu'il est correctement paramétré, il est principalement limité par les capacités de calcul de la machine. Ce test de performance est alors peu représentatif du comportement des codes de simulation, mais permet tout de même d'évaluer une borne supérieure des capacités de calcul brutes atteignables par une machine.

<sup>&</sup>lt;sup>8</sup>Benchmark en anglais.

<sup>&</sup>lt;sup>9</sup>**FLOP/s**: FLoating point Operations Per Second.

FIGURE 1.1 – Évolution des performances de la première (N=1) et de la dernière machine (N=500) du classement TOP500 (source : top500.org).

Outre le développement des supercalculateurs, les micro-ordinateurs se sont démocratisés et sont progressivement apparus dans les entreprises, dans les laboratoires de recherche et chez les particuliers. Cette adoption massive a contribué à leur amélioration et à la diminution de leur coût de fabrication grâce à une commercialisation à grande échelle. Certains organismes ne disposaient pas des moyens financiers suffisants pour acquérir un supercalculateur de l'époque. Une parade, anticipée par Gene Amdahl en 1967, consistait à combiner la puissance de calcul de plusieurs ordinateurs personnels [15]. Cette façon de procéder a été adoptée pour entreprendre le projet Beowulf [16] qui a abouti à l'assemblage d'une machine par la NASA<sup>10</sup> en 1994. Celle-ci offrait une meilleure flexibilité d'évolution en reliant, à titre d'exemple, un plus grand nombre d'ordinateurs basés sur des composants standards. L'amélioration des interconnexions à la fin des années 90 a amorcé un tournant dans la façon dont les superordinateurs étaient élaborés. De nouveaux supercalculateurs, composés de puissants ordinateurs, ou nœuds de calcul, physiquement reliés en grappes<sup>11</sup>, apparaissent alors. En juin 2013, la majorité des machines classées au TOP500 étaient basées sur une architecture de type grappe de calcul. Chaque nœud repose sur une agrégation de plusieurs technologies acquises et améliorées à différentes périodes de l'histoire de l'évolution des machines. Au fil du temps, les supercalculateurs deviennent de plus en plus puissants, mais, en contrepartie, ils se complexifient.

En premier lieu, ce chapitre esquissera les besoins en puissance des programmes de simulations. En second lieu, il abordera les grandes étapes de l'évolution des machines afin d'appréhender les contraintes imposées par les technologies associées. Enfin, en dernier lieu, seront évoquées certaines spécificités des machines contemporaines.

<sup>&</sup>lt;sup>10</sup>**NASA**: National Aeronautics and Space Administration.

<sup>&</sup>lt;sup>11</sup>Cluster en anglais.

#### 1.1 La puissance de calcul pour la simulation numérique

La simulation numérique vise majoritairement à reproduire des phénomènes physiques. En s'appuyant sur les recherches fondamentales, de nouveaux enjeux sont apparus. Elle est rapidement devenue inévitable dans divers domaines pour résoudre des problèmes intenses en calcul. Cependant, la simulation n'est pas que du calcul, c'est aussi le fruit de l'association de diverses compétences qui ne se résument pas à l'informatique. Il faut dans un premier temps élaborer un modèle physique des phénomènes étudiés et analyser les équations associées. La conception d'algorithmes permet seulement ensuite d'exprimer la façon dont les machines vont résoudre ces équations via le calcul numérique. Il s'agit de décrire cette résolution (éventuellement réajuster la modélisation) pour exploiter efficacement les supercalculateurs qui sont devenus massivement parallèles. Enfin, la précision et la validité des solutions obtenues par la simulation doivent être évaluées pour s'assurer qu'elles sont bien représentatives du cadre d'étude considéré.

Dans l'industrie, les simulations interviennent souvent pour minimiser le recours à des moyens coûteux comme la production de maquettes et de prototypes. Il est moins onéreux de concevoir un modèle adéquat et de l'étudier sur un ordinateur que de mettre en place une série d'épreuves réelles. En aéronautique, le comportement d'un profil d'aile d'avion peut être étudié afin de maximiser sa portance, sans avoir à la construire. Dans les phases d'exploration de l'industrie pétrolière, elle sert à extrapoler les données sismiques en aiguillant les géologues afin de limiter les forages coûteux et difficilement accessibles pour se focaliser sur les sites les plus profitables. Les simulations peuvent aussi accélérer le temps et anticiper certains phénomènes. En astrophysique, elles permettent en particulier de recréer de longs phénomènes inaccessibles autrement. Le projet DEUS<sup>12</sup> [17] aspire à reconstituer numériquement la formation de l'univers pour comprendre la nature de l'énergie noire. Les prévisions météorologiques possèdent des contraintes de précision et également de rapidité d'exécution. Il s'agit de prévoir le temps qu'il fera dans un futur très proche en tenant compte d'une grande quantité de paramètres relevés par les stations. À un tout autre ordre de grandeur, les simulations ont conduit à l'élaboration de composants électroniques plus performants. En science des matériaux, il est possible d'agir sur les différents paramètres à l'échelle des molécules et des atomes. Des calculs qualifiés d'ab initio sont en plein essor et consistent à retrouver les propriétés des matériaux en se basant sur la physique atomique. Ils permettent de s'affranchir de données expérimentales qui pouvaient servir de postulats et de paramètres pour étudier des phénomènes plus conséquents. Par ailleurs, les simulation participent à réduire les risques d'accidents en étudiant des phénomènes dangereux. Des modélisations de tsunamis sont par exemple réalisées dans le cadre de prévention pour déterminer les zones potentiellement exposées.

Ainsi, la simulations numérique sert à étudier les propriétés de systèmes modélisés et d'anticiper leur évolution. Elle permet d'aller au-delà du couple classique constitué de la théorie et de l'expérimentation, en explorant une plus grande quantité de possibilités. "La simulation est une extension ou une généralisation de l'expérience" selon l'académicien Michel Serres [18]. Elle permet de grossir les espaces, d'accroître la vitesse du temps, d'augmenter ou de diminuer les interactions et les contraintes. Elle peut approcher des phénomènes de plus en plus complexes en s'appuyant sur des capacités de traitements toujours plus conséquentes. L'amélioration des superordinateurs comble progressivement ces besoins de puissance. Cependant, ces machines tendent à se complexifier. Étudier leurs évolutions nous aide à comprendre la technologie actuelle.

<sup>&</sup>lt;sup>12</sup>**DEUS**: Dark Energy Universe Simulation.

#### 1.2 Les architectures parallèles et l'évolution des supercalculateurs

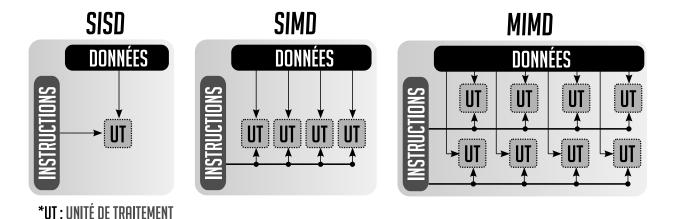

En 1966, Michael J. Flynn propose une classification [19] des architectures en fonction des types d'opérations. Celles-ci sont caractérisées par le nombre d'instructions et la quantité de flots de données impactés par ces traitements. Les supercalculateurs actuels reposent sur plusieurs catégories via divers mécanismes, héritages des technologies développées au cours de l'évolution des machines. Cette section retrace les principales avancées en s'appuyant sur la taxonomie de Flynn.

FIGURE 1.2 – Taxonomie de Flynn (Le modèle MISD n'est pas représenté, car peu employé).

#### 1.2.1 Des machines séquentielles aux grappes de calcul

Les premières machines dites *scalaires* fonctionnaient séquentiellement, c'est-à-dire qu'une instruction modifiait un flux de données à la fois. Il s'agit de la catégorie la plus élémentaire appelée *SISD*<sup>13</sup> de la classification de Flynn (cf. figure 1.2). En 1962, la machine ATLAS [20] de l'université de Manchester et Ferranti accélère les opérations *SISD* en ouvrant la voie au *parallélisme d'instructions*<sup>14</sup>. Ce fut la première machine à employer des techniques similaires à celles élaborées par Henry Ford dans le domaine de l'automobile. Un *pipeline d'exécution*, sorte de ligne de production, accroît le rendement des opérations en permettant une exécution simultanée de plusieurs sous étapes d'une instruction. Les travaux de Seymour Cray, Jim Thornton et Dean Roushde de l'entreprise CDC<sup>15</sup> ont permis d'améliorer davantage les performances [21]. En 1963, le *CDC-6600* [22] est considéré comme le premier supercalculateur. C'est la première machine *super-scalaire*. Elle rend possible l'exécution de plusieurs instructions simultanément grâce à diverses unités de traitement. Elle était plus de dix fois plus performante que ses concurrentes à sa sortie, et elle restera la machine la plus puissante au monde jusqu'en 1969. Depuis, les traitements *SISD* ont été améliorés en combinant des techniques permettant de gérer plus de parallélisme d'instructions.

Dans les années 70, des supercalculateurs sont capables de traiter plusieurs flots de données à partir d'une même instruction; c'est l'hégémonie des machines *vectorielles* [23]. Ces architectures *SIMD*<sup>16</sup> (cf. figure 1.2) émergent avec le *CDC STAR-100* [24] et le *TI-ASC* [25]. Celles-ci restent toutefois plus lentes que les machines contemporaines purement *super-scalaires*. En 1972, Seymour Cray quitte *CDC* et fonde *Cray Research* dont le premier produit en 1975 fut le *Cray-1* [26], un des supercalculateurs les plus renommés de l'histoire, combinant opérations vectorielles et

<sup>&</sup>lt;sup>13</sup>**SISD**: Single Instruction, Single Data.

<sup>&</sup>lt;sup>14</sup>**ILP**: Instruction Level Parallelism.

<sup>&</sup>lt;sup>15</sup>**CDC**: Control Data Corporation.

<sup>&</sup>lt;sup>16</sup>**SIMD**: Single Instruction, Multiple Data.

parallélisme d'instructions. Des emplacements mémoires plus rapides, appelés *registres*, sont positionnés physiquement plus proches des unités de calcul. Ils permettent de réduire les temps d'accès aux données réutilisées plusieurs fois d'affilée par rapport à des opérations directement effectuées en mémoire centrale. De nos jours, les processeurs modernes pour le marché grand public, de même que ceux dédiés au calcul, embarquent des registres et des unités de calcul vectorielles accessibles par des instructions de bas niveau.

Des machines constituées de plusieurs processeurs sont apparues dans les années 70. Des flots d'instructions différents pouvaient être réalisés simultanément sur plusieurs flots de données, permettant ainsi un traitement de type *MIMD*<sup>17</sup> (cf. figure 1.2). Ces premières machines multi-processeurs sont pour la plupart dites asymétriques (AMP<sup>18</sup>) puisque chaque processeur possédait sa propre mémoire, ainsi que des propriétés d'accès aux périphériques distinctes. À titre d'exemple, le deuxième processeur que pouvait héberger la machine VAX-11/782 n'était pas connecté aux périphériques d'entrées/sorties [27]. Ces processeurs supplémentaires étaient généralement considérés comme des extensions afin d'augmenter, à moindre frais, les capacités de calcul. Les systèmes d'exploitation de l'époque étaient cependant développés pour un unique processeur central et ne permettaient pas de contrôler efficacement plusieurs processeurs à la fois. Des machines symétriques (SMP<sup>19</sup>), plus aisées à programmer, ont progressivement remplacé les systèmes asymétriques. Les processeurs qui composaient ces nouvelles architectures étaient alors fortement couplés. Ils partageaient la même mémoire, possédaient un plein accès à toutes les entrées/sorties et étaient pilotés par un unique système d'exploitation. De 1982 à 1985, le Cray X-MP [28] fut la machine la plus puissante au monde. Elle intégrait deux processeurs basés sur des améliorations du Cray-1, lesquels étaient exploités de manière symétrique autour d'une mémoire commune. Dans les années 90, des machines massivement parallèles, constituées de centaines, voire de milliers d'unités de calcul indépendantes sont développées. Le CM-5 [29], commercialisé en 1992 par Thinking Machines Corporation, en est un exemple avec ses 1024 processeurs. Inspiré par le projet Beowulf, à l'origine des architectures en grappes à base de composants standards, la machine ASCI Red [30] réunissait 4510 nœuds de calcul, chacun constitué d'une mémoire distincte et de deux processeurs. Lors de sa construction en 1996, c'était le premier supercalculateur à dépasser le millier de milliards d'opérations par secondes (TFLOP/s) au test de performance *Linpack*.

Depuis, les assemblages par *grappes* se sont répandus, combinant la puissance de nombreux nœuds de calcul et embarquant plusieurs processeurs. Chaque nouvelle génération de machine pouvait à la fois augmenter sa quantité de processeurs interconnectés et profiter de l'amélioration de leurs performances. Dans les années 2000, plusieurs limitations technologiques ont cependant contraint les fondeurs à modifier la façon dont les processeurs étaient élaborés.

#### 1.2.2 La révolution des processeurs multi-cœurs

Les fondeurs, tels qu'Intel et AMD, profitaient du doublement de la densité des puces prévu par la loi de Moore afin d'accroître les performances des processeurs. Deux leviers permettaient cela, grâce, d'une part à l'amélioration des microarchitectures pour un meilleur parallélisme d'instructions, et d'autre part à l'élévation de la *fréquence d'horloge*, ce qui permettait d'accélérer la cadence d'exécution des calculs. Depuis le début des années 2000, ces deux facteurs de performance ont rencontré des limitations majeures.

<sup>18</sup>**AMP**: Asymmetric Multi-Processing.

<sup>19</sup>**SMP**: Symmetric Multi-Processing.

<sup>&</sup>lt;sup>17</sup>**MIMD**: Multiple Instruction, Multiple Data.

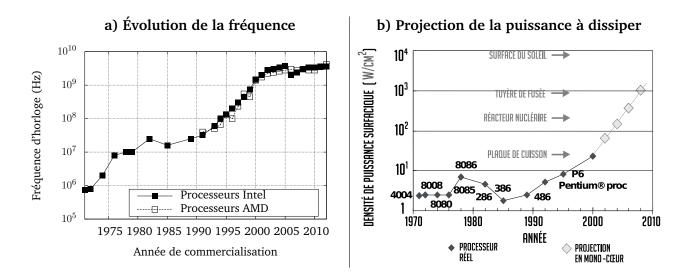

FIGURE 1.3 – a) Évolution de la fréquence des microprocesseurs. b) Projection de la puissance surfacique des microprocesseurs avant l'introduction des multi-cœurs (source : S. Borkar, Intel).

La fréquence d'horloge des processeurs est passée de *740 kHz* (740 mille cycles par seconde) en 1971 à environ *3 GHz* (3 milliards de cycles par seconde) en 2004. Huit ans plus tard, cette fréquence n'avait globalement pas progressé comme l'illustre la figure 1.3a. Pour comprendre la cause de cette stagnation, il faut s'intéresser au fonctionnement physique des processeurs. Ceux-ci sont des composants très denses constitués de transistors. Un transistor est un élément électronique à deux états, ouvert ou fermé, pour représenter une information binaire. Le pic de consommation d'énergie est obtenu lorsqu'il change d'état. Or, dans un processeur, les transistors passent justement leur temps à changer d'état; la vitesse de commutation étant cadencée par la fréquence d'horloge. Plus les transistors commutent rapidement, plus l'énergie consommée est importante. L'équation de la puissance dynamique d'un transistor peut être écrite de la manière suivante :

$$P = K \times (\text{capacit\'e de charge}) \times (\text{tension})^2 \times (\text{fr\'equence de commutation})$$

La théorie du passage à l'échelle de Dennard [31] anticipait une meilleure efficacité des transistors lorsque ceux-ci étaient gravés plus finement. Il était ainsi possible de réduire la *tension* et la *capacité de charge*. Couplée à la loi de Moore, elle prévoyait un doublement du nombre de transistors tous les deux ans et une élévation de la fréquence de 40% en conservant une puissance électrique équivalant à la génération précédente. Depuis le début des années 2000, la théorie de Dennard n'est plus applicable. Une butée technologique a été atteinte, appelée *mur de la puissance*. Augmenter la fréquence des processeurs implique désormais inévitablement une élévation de la puissance consommée. Une grande partie de celle-ci est transformée en chaleur qu'il faut dissiper pour ne pas entraîner la destruction du composant. Pendant un temps, une parade a permis de continuer à augmenter la fréquence d'horloge en employant des dissipateurs et des ventilateurs de plus en plus conséquents. Cette solution a rapidement atteint ses limites, car la puissance à dissiper augmentait à une allure folle. La figure 1.3b est une projection pessimiste en 2000 de l'ampleur de la puissance thermique à évacuer en conservant la même vitesse d'évolution, sans rupture technologique.

Presque à la même période, le parallélisme d'instructions atteignait également ses limites. Il était de plus en plus compliqué d'extraire du parallélisme d'un flux d'instructions. En 2004, la version Prescott du processeur Intel Pentium 4 intégrait un plus long pipeline, destiné à accroître le rendement des opérations effectuées. Ses 31 étages permettaient également d'atteindre de plus hautes fréquences d'horloge. Ce pipeline divisait les instructions en un plus grand nombre de sous-instructions élémentaires dont chacune pouvait fonctionner à une cadence plus élevée. Hélas les performances de nombreux codes de calcul étaient dégradées, notamment à cause de l'association des nombreux étages à d'autres fonctionnalités du parallélisme d'instructions, comme les exécutions spéculatives liées aux instructions de branchement. Lors d'une mauvaise prise de décision par anticipation, les efforts accumulés dans le pipeline sont abandonnés afin de réorienter les calculs vers une solution correcte. La longueur du pipeline rallonge ainsi le délai de complétude des premières instructions, entraînant finalement des performances mitigées. Intel prévoyait également une élévation de la fréquence de fonctionnement de cette microarchitecture jusqu'à 10 GHz. Les courants de fuite à l'origine de la fin de la théorie de Dennard n'ont permis d'atteindre qu'une fréquence de 3,8 GHz, aux prix d'une élévation importante de l'enveloppe thermique. Cette dernière avoisinait les 100 Watts à dissiper, contre moins de la moitié pour les processeurs Pentium 3 de génération précédente. Le successeur du Pentium 4, lequel devait être commercialisé en 2005, a été abandonné à cause de son enveloppe thermique trop élevée de 150 Watts [32].

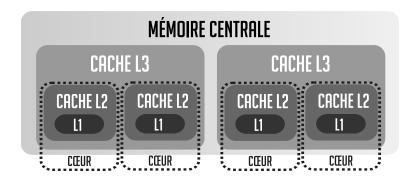

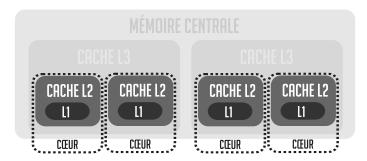

Une nouvelle façon d'améliorer les performances des processeurs était nécessaire. Il ne fallait ni compter sur une nette élévation de la fréquence d'horloge, afin de conserver une enveloppe thermique acceptable, ni attendre des progrès significatifs du *parallélisme d'instructions*. Le solution adoptée dès 2005 fut d'intégrer l'équivalent de plusieurs processeurs, appelés *cœurs de calcul*, sur un même circuit intégré<sup>20</sup>. En réduisant leur fréquence de fonctionnement, il était possible de combiner les capacités de calcul de plusieurs processeurs sur une puce, sans augmenter la puissance thermique à dissiper. Leur exploitation est ainsi comparable au recours à plusieurs processeurs dans un même nœud de calcul, en suivant un mode de fonctionnement de type *MIMD*. Ces *processeurs multi-cœurs* peuvent cependant comporter des circuits particuliers, afin de faciliter la communication entre les cœurs de calcul et participent à la complexification de la mémoire des machines, laquelle sera abordée dans le prochain chapitre.

#### 1.2.3 Les accélérateurs massivement parallèles

Des matériels spécialisés sont parfois employés pour accélérer certains traitements. Basés sur des circuits intégrés dédiés, ces accélérateurs sont plus efficaces pour certaines fonctionnalités que les processeurs généralistes (CPU<sup>21</sup>). Ces coprocesseurs sont rattachés à une *carte fille* en tant qu'extension d'un nœud de calcul ou intégrés dans la même puce que le *CPU* en formant un processeur accéléré appelé *APU*<sup>22</sup>. Autrefois, les coprocesseurs pouvaient être directement connectés à la carte mère, comme c'est toujours le cas pour le *CPU*. Le recours à ces puces spécialisées est relativement ancien puisque des coprocesseurs étaient déjà employés dans les années 1960 avec la machine *Solomon* [33] afin d'améliorer les capacités de traitement vectoriel.

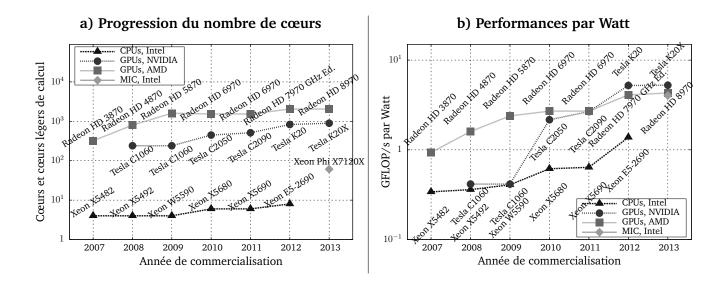

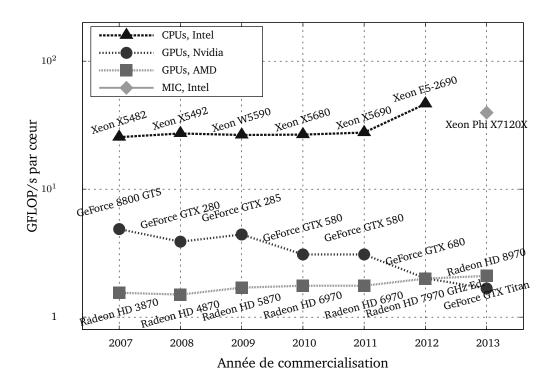

De nos jours, les accélérateurs sont majoritairement dérivés de processeurs graphiques  $(GPU^{23})$ . Des variantes peuvent être dénombrées, telles que les coprocesseurs possédant une microarchitecture plus proche des CPUs, mais intégrant beaucoup plus de cœurs de calcul que ceux-ci  $(MIC^{24})$  ou Intel Xeon Phi). Les accélérateurs actuels détiennent essentiellement une

<sup>23</sup>**GPU**: Graphics Processing Unit.

<sup>24</sup>**MIC**: Many Integrated Core.

<sup>&</sup>lt;sup>20</sup>Die en anglais.

<sup>&</sup>lt;sup>21</sup>**CPU**: Central Processing Unit.

$<sup>^{22} \</sup>mathrm{APU}$  : Accelerated Processing Unit.

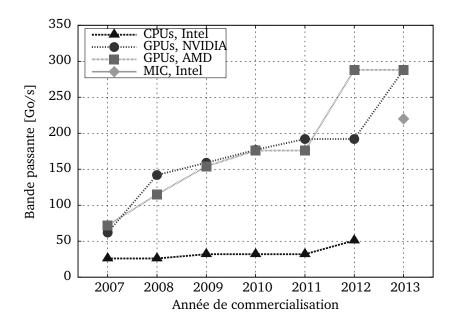

microarchitecture massivement multi-cœurs, c'est à dire intégrant plusieurs dizaines ou centaines de cœurs de calcul<sup>25</sup> comme le démontre la figure 1.4a. Chacun de ces cœurs possède des capacités de calcul vectoriel accrues grâce à de larges unités ou à l'emploi de plusieurs cœurs légers fonctionnant en mode *SIMD*. Tout comme les processeurs généralistes multi-cœurs, ces accélérateurs combinent donc des mécanismes de types *MIMD* et *SIMD*, mais permettent d'atteindre des capacités de traitement bien plus avantageuses au regard de la consommation électrique (cf. figure 1.4b). Les principaux coprocesseurs sont présentés dans cette sous-section.

FIGURE 1.4 – Caractéristiques de calcul en double précision des CPUs, GPUs et MIC (source [34]).

#### Les générations antérieures d'accélérateurs et alternatives

Les *FPGAs*<sup>26</sup> ont été conçus par l'entreprise Xilinx en 1985. Contrairement aux processeurs généralistes ou aux puces dédiées à des applications spécifiques (ASICs<sup>27</sup>), la structure de leur circuit n'est pas figée. Les FPGAs possèdent des blocs logiques qui peuvent être reconfigurés matériellement au moyen d'un langage de description d'agencement électronique tels que *VHDL*<sup>28</sup> ou *Verilog*. Le câblage de ces blocs peut être modifié à volonté, permettant ainsi d'adapter le circuit pour effectuer des traitements spécifiques. Ils sont généralement moins performant que les puces ASICs, mais du fait de leur capacité de reprogrammation, ils servent souvent à concevoir ces derniers. En 2004, des FPGAs ont été intégrées à la machine *Cray XD1* aux côtés de processeurs généralistes *AMD Opteron* et peuvent entre autres servir à accélérer des opérations d'algèbre linéaire [35, 36]. La machine *Maxwell* a été élaborée à l'université d'Édinburgh plus tard, en 2007, pour du calcul généraliste. Elle est quant à elle constituée d'un assemblage de 64 FPGAs [37]. Cependant, en plus d'être très onéreux, la programmation des FPGAs reste complexe. Peu de machines de production les ont adoptés pour du calcul intensif généraliste. Les progrès dans le domaine du *calcul à haute performance reconfigurable* (HPRC<sup>29</sup>) pourraient toutefois les amener sur le devant de la scène dans les années avenir.

<sup>&</sup>lt;sup>25</sup>Many-Cores en anglais.

<sup>&</sup>lt;sup>26</sup>**FPGA**: The Field-Programmable Gate Arrays.

<sup>&</sup>lt;sup>27</sup>**ASIC**: Application-Specific Integrated Circuit.

<sup>&</sup>lt;sup>28</sup>**VHDL**: VHSIC Hardware Description Language.

<sup>&</sup>lt;sup>29</sup>**HPRC**: High Performance Reconfigurable Computing.

Les cartes accélératrices de l'entreprise *Clearspeed* [38] intègrent une puce **ASIC** pour accélérer des traitements dans le domaine du calcul à haute performance. En novembre 2006, le supercalculateur japonais *Tsubame*, alors  $9^e$  au classement *TOP500*, embarque 360 de ces accélérateurs pour accroître les performances de cette machine de 24% en élevant la consommation électrique de seulement 1%. Depuis 2008, un processeur spécialisé *CSX700*, constitué de 192 cœurs légers, est capable de fournir une puissance de calcul théorique de 96 GFLOP/s pour 25 Watts de consommation lorsqu'il est associé à une capacité de 2 Go de mémoire sur une carte accélératrice. Ces processeurs ne sont cependant pas commercialisés en grand nombre ce qui a tendance à les rendre financièrement moins abordables que d'autres solutions. Depuis 2009, l'entreprise Clearspeed cherche à étendre son offre au secteur des systèmes embarqués, et plus particulièrement aux projets qui nécessitent une puissance de calcul substantielle.

En 2005, *Sony, Toshiba* et *IBM* dévoilent le processeur *Cell* [39]. Il s'agit d'une puce hétérogène embarquant des cœurs de calcul de différents types. Cette architecture peut être qualifiée d'*APU* puisqu'un cœur généraliste (PPE<sup>30</sup>) est épaulé par huit cœurs de calcul spécialisés (*SPE*<sup>31</sup>) comportant des jeux d'instructions vectorielles. Chaque *SPE* possède une mémoire locale de faible capacité pour permettre le déport des données et des instructions de calcul. Les programmeurs sont contraints à gérer explicitement ces mémoires, ce qui participe à rendre difficile l'exploitation de ce processeur. Le *Cell* équipe la *PlayStation 3*, une console de jeux vidéo commercialisée par Sony, ce qui le rend plus attractif financièrement pour le domaine du calcul scientifique. En juin 2008, *Roadrunner* [40] était la machine la plus puissante du monde en embarquant à la fois 6 480 processeurs généralistes multi-cœurs de marque *AMD* et 12 960 processeurs Cell. C'est le premier supercalculateur à dépasser le million de milliards d'opérations par seconde (PFLOP/s) au *TOP500*. Sa capacité de calcul était plus de deux fois supérieure à la deuxième machine et détenait une des meilleures efficacités énergétiques du classement. Le Cell cédera progressivement sa place aux processeurs graphiques dans le domaine du calcul à haute performance.

#### Les GPUs

Les premiers processeurs graphiques étaient employés pour piloter un écran et décharger le CPU de certaines opérations qui permettaient un affichage à deux dimensions. Dans les années 1990, des cartes d'extensions ont fait leur apparition pour accélérer cette fois-ci les rendus à trois dimensions. La série Voodoo, élaborée par la société 3dfx Interactive, fut très populaire pour améliorer la qualité des rendus graphiques dans les jeux vidéos. A cette époque, les cartes graphiques 2D étaient vendues séparément de ces cartes accélératrices 3D, chacune d'entre elles embarquait ainsi un processeur spécialisé. En 1996, l'entreprise canadienne ATI (acquise par AMD en 2006) commercialise la ATI Rage, première carte intégrant les deux capacités 2D et 3D. En 2000, le concurrent Nvidia rachète 3dfx Interactive après avoir dévoilé le processeur graphique Geforce 256. Le terme de GPU [41] est alors évoqué pour la première fois et désigne un composant complexe capable d'effectuer de nombreux traitements visuels. Ces premiers GPUs étaient peu exploités en dehors des jeux vidéo et de l'infographie. Ils intégraient des unités des traitements matériels très spécialisées (FPP<sup>32</sup>). Grâce à plusieurs étapes, ces unités spécifiques permettaient plusieurs modifications visuelles, avant de les combiner pour former l'image finale. Cette technique n'offrait cependant pas une souplesse suffisante pour s'adapter efficacement aux évolutions des effets graphiques.

<sup>32</sup>**FPP**: Fixed Function Pipeline.

<sup>&</sup>lt;sup>30</sup>**PPE**: PowerPC Processing Element.

$<sup>^{31}{</sup>m SPE}$  : Synergistic Processing Element.

En 2001, avec la carte *Nvidia Geforce 3*, les GPUs évoluent pour supporter des techniques de post-traitement plus sophistiquées, en s'adaptant aux programmes par *shaders* qui permettent de mieux paramétrer une partie des opérations de rendu. Une plus grande souplesse était ainsi permise en gagnant en généricité par l'emploi d'unités de traitement matérielles propres aux trois types de "*shaders*" usuels<sup>33</sup>. La puissance de calcul des GPUs devient de plus en plus conséquente grâce à une grande capacité de traitements parallèles. De plus, l'emploi massif des GPUs dans les consoles de jeu et dans les ordinateurs a contribué à fortement réduire leur coût. Les scientifiques commencent à s'y intéresser pour accélérer des traitements dans d'autres domaines. La pratique GPGPU<sup>34</sup> émerge [42]. Elle consiste a détourner l'utilisation spécialisée d'un GPU vers du calcul générique.

Depuis, les processeurs graphiques ont unifié les unités de traitement shaders en permettant une meilleure gestion des ressources matérielles et une plus grande souplesse d'exploitation. Les GPUs adoptent des architectures massivement parallèles en embarquant une capacité de traitements conséquente, regroupée dans des unités de calcul multi-cœurs. Chaque constructeur adopte des approches diverses. Les architectures d'ATI/AMD intègrent des cœurs à larges instructions vectorielles tandis que celles de Nvidia comportent de nombreux cœurs légers exploités de manière SIMD. Ces unités de traitement, d'élaborations distinctes, sont appelées processeur de flux (SP<sup>35</sup>). Des modèles de programmation plus accessibles ont permis d'accroître davantage le recours aux GPUs pour du calcul générique [43]. Ils intègrent des améliorations qui les rendent plus attractifs pour le calcul scientifique tels que le support du calcul à double précision, des mémoires à correction d'erreurs matérielles (ECC<sup>36</sup>) ou des communications complètement asynchrones avec la mémoire centrale. Depuis 2010, plusieurs noyaux de calcul peuvent s'exécuter de manière simultanée sur des unités multi-cœurs distinctes avec l'architecture Fermi [44, 45] de Nvidia. Les GPUs possèdent désormais un mode de fonctionnement mixte MIMD et SIMD. En novembre 2010, la machine chinoise Tianhe-1A devient le premier supercalculateur au classement TOP500 en reposant sur 14336 CPUs Intel et 7168 GPUs Nvidia.

#### Les MICs

En 2009, *Intel* annonce le processeur *Larrabee* [46], une puce semblable à un GPU basée sur de nombreux cœurs de calcul similaires à ceux employés dans les CPUs généralistes *x86/64*. Cependant, la solution n'est pas viable commercialement en raison de ses performances décevantes. La microarchitecture a été améliorée en s'appuyant également sur d'autres projets<sup>37</sup> pour aboutir aux MICs. *Intel* ne vise désormais que le marché du calcul à haute performance avec son premier produit commercialisé en 2012, baptisé *Xeon Phi*. Ce dernier embarque un système d'exploitation, ce qui peut lui octroyer une plus grande autonomie vis-à-vis des CPUs. Il est également composé de 61 cœurs de calcul<sup>38</sup>, connectés en anneau et comportant chacun de larges instructions vectorielles de 512 bits. Cette solution est censée offrir une compatibilité des logiciels développés pour des CPUs, là où les GPUs requièrent une réécriture complète du code. *Intel* mise ainsi sur la productivité et la programmabilité en permettant un portage fonctionnel rapide. En juin 2013, *Tianhe-2* est la machine la puissante au monde en agrégeant seize-mille nœuds de calculs, comportant chacun deux CPUs et trois Xeon Phi [12] d'*Intel*. Ce supercalculateur totalise ainsi plus de trois millions de cœurs de calcul.

<sup>&</sup>lt;sup>33</sup>Vertex shaders, Geometry shaders et Pixel shaders.

<sup>&</sup>lt;sup>34</sup>**GPGPU**: General Purpose Graphics Processing Unit.

<sup>&</sup>lt;sup>35</sup>**SP**: Stream Processors.

<sup>&</sup>lt;sup>36</sup>**ECC**: Error Checking and Correcting.

<sup>&</sup>lt;sup>37</sup>Teraflops Research Chip [47] et Intel Single-Chip Cloud.

<sup>&</sup>lt;sup>38</sup>Dont un cœur dédié à l'OS.

#### 1.3 Les supercalculateurs contemporains

Les machines les plus puissantes, élaborées après 2008, sont pour la plupart de classe "pétaflopique" (10<sup>15</sup> FLOP/s), c'est-à-dire qu'elles sont capables d'effectuer plus d'un million de milliards d'opérations par seconde [48]. La machine du *CEA-DAM Tera-100* (cf. figure 1.5a) est un exemple de ce genre de supercalculateur. Produite par la société française *BULL*, elle est mise en service en 2010 pour 1,254 PFLOP/s théorique. Elle se positionne sixième au *TOP500* en novembre 2010 en atteignant 1,05 PFLOP/s et était également la machine la plus puissante d'Europe. *Curie* (cf. figure 1.5b) a été financé par le *Grand Équipement National de Calcul Intensif* (GENCI) et est hébergé dans les locaux du *Très Grand Centre de Calcul* au CEA. C'est un supercalculateur ouvert aux scientifiques européens dans le cadre de la participation aux infrastructures PRACE<sup>39</sup>. Il a également été installé par *Bull* et accède à la neuvième place du *TOP500* avec 1,359 PFLOP/s en juin 2012.

FIGURE 1.5 – Exemples de deux supercalculateurs pétaflopiques français.

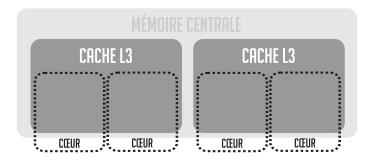

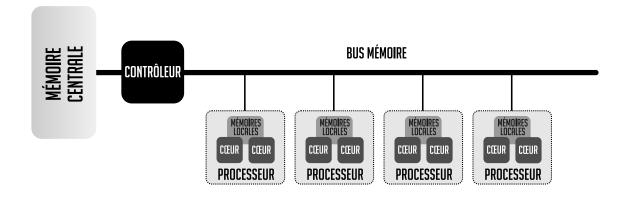

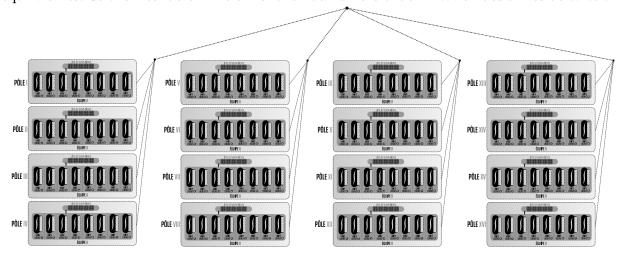

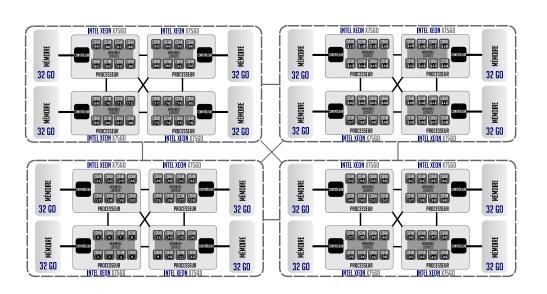

L'élaboration d'un supercalculateur petaflopique requiert un effort particulier d'intégration pour contenir une forte densité de composants, tout en assurant une dissipation thermique adéquate. Comme l'illustre la figure 1.6, Tera-100 est une machine organisée en une grappe de 4370 nœuds de calcul, répartis dans 220 armoires. Chaque nœud contient 4 processeurs octo-cœurs. Tera-100 totalise ainsi 139 840 coeurs de calcul, 300 To de mémoire vive et possède un stockage d'une capacité de 20 Po.

FIGURE 1.6 – Intégration des ressources de calcul en grappe. Exemple de Tera-100.

<sup>&</sup>lt;sup>39</sup>**PRACE**: Partnership for Advanced Computing in Europe.

#### 1.3.1 L'émergence des grappes de calcul hétérogènes

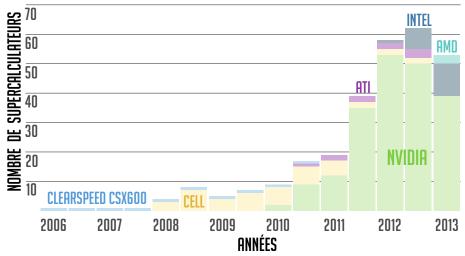

Des supercalculateurs intégrant des accélérateurs matériels apparaissent à partir de 2006 et constituent désormais une part non négligeable des machines classées au *TOP500* (cf. figure 1.7).

FIGURE 1.7 – Nombre de supercalculateurs du *TOP500* comportant des accélérateurs (source : top500.org).

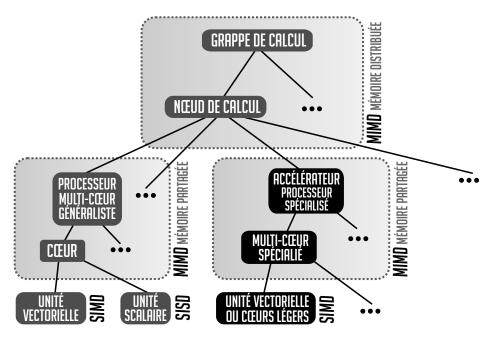

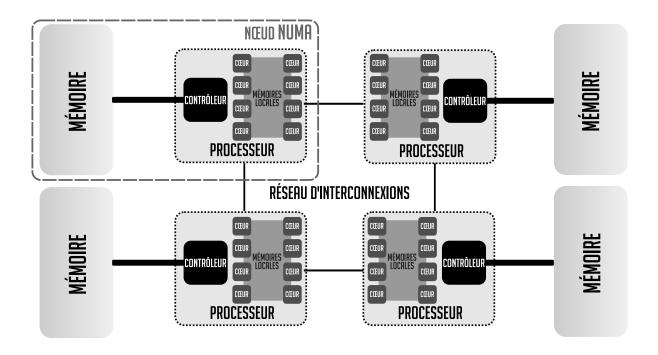

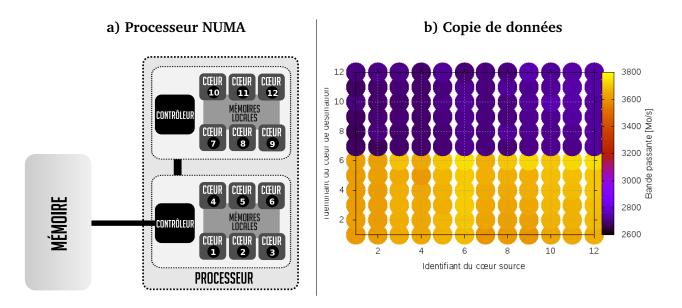

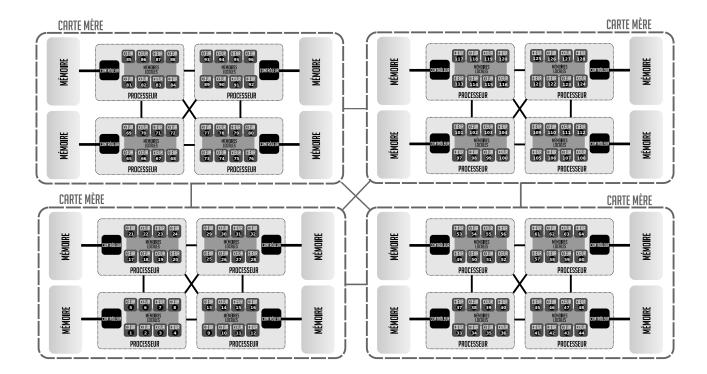

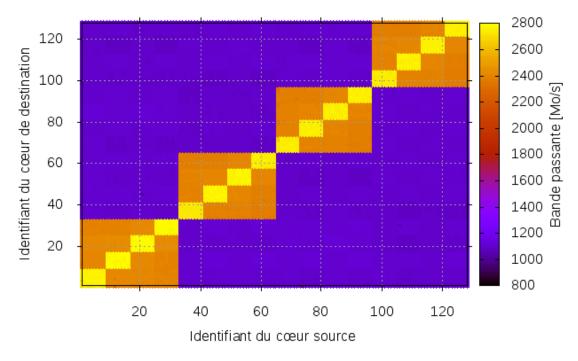

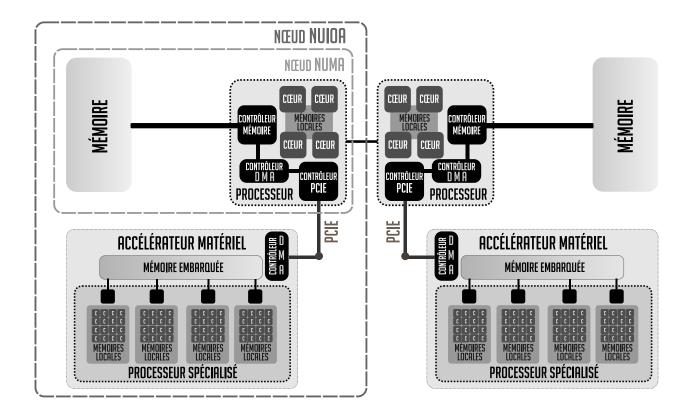

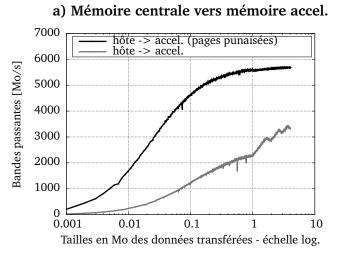

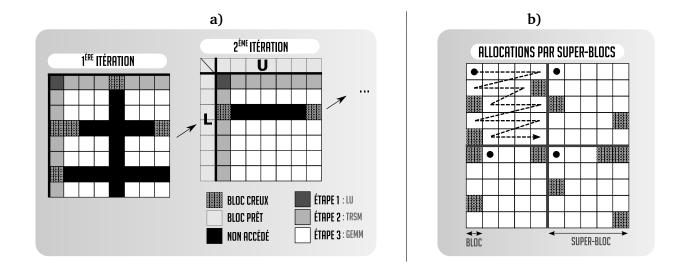

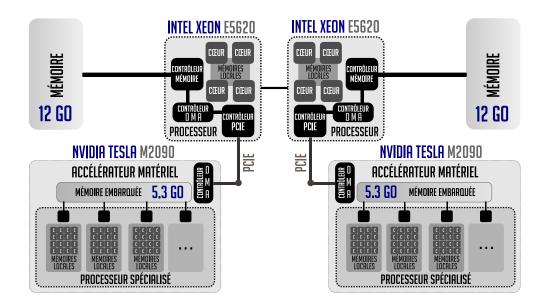

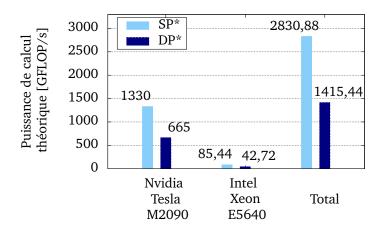

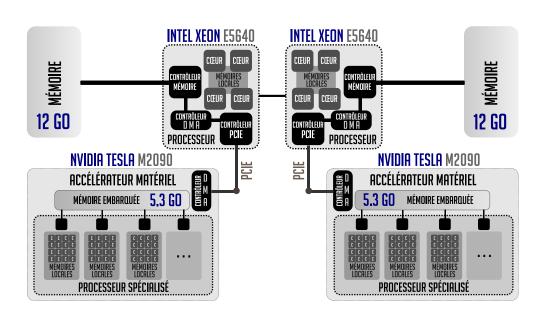

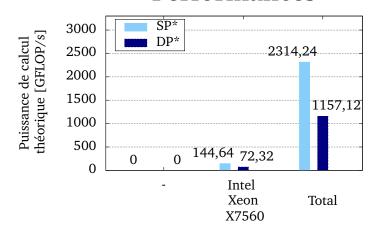

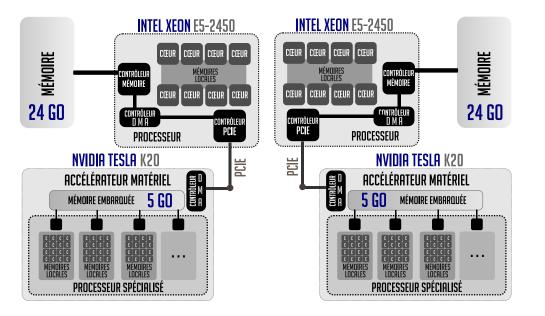

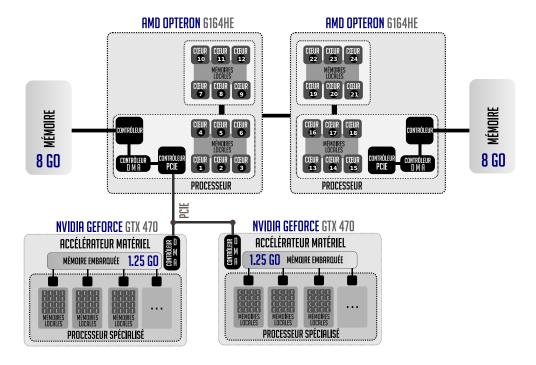

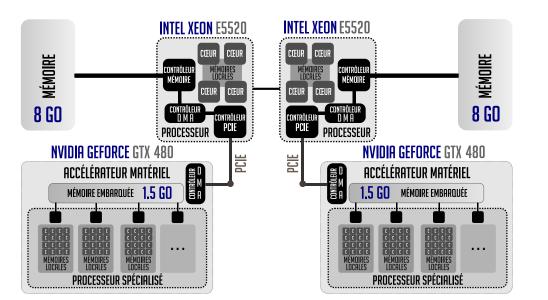

En 2011, une partition de 192 nœuds hétérogènes est rattachée à Tera-100. Chaque nœud est alors constitué de deux CPUs quadricœurs *Intel* et deux GPUs *Nvidia*. Les machines hétérogènes agrègent ainsi plusieurs technologies développées tout au long de l'histoire des superordinateurs. Les processeurs réalisent des opérations de type *SISD* et *SIMD*. Leurs assemblages dans un nœud, ainsi que la démultiplication du nombre de cœurs, permettent un fonctionnement *MIMD* à mémoire partagée, alors que l'ensemble de tous les nœuds repose sur un mécanisme *MIMD* à mémoires distribuées. Les accélérateurs matériels, quant à eux, combinent *MIMD* à mémoire partagée et *SIMD* avec leurs cœurs légers ou leurs instructions vectorielles. La figure 1.8 résume l'imbrication de ces diverses architectures dont chacune nécessite généralement un modèle de programmation distinct, plus adapté aux contraintes liées à leur exploitation.

FIGURE 1.8 – Supercalculateur en grappes avec nœuds de calcul hétérogènes. Types de traitements de chaque assemblage selon la taxonomie de Flynn.

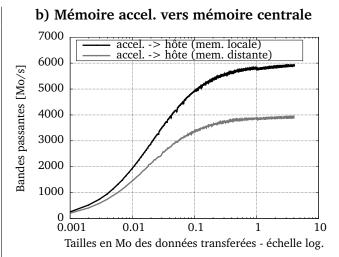

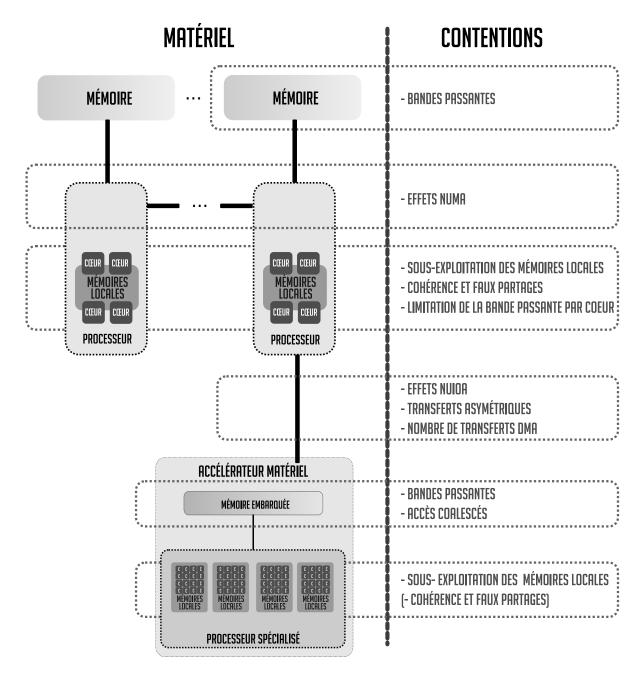

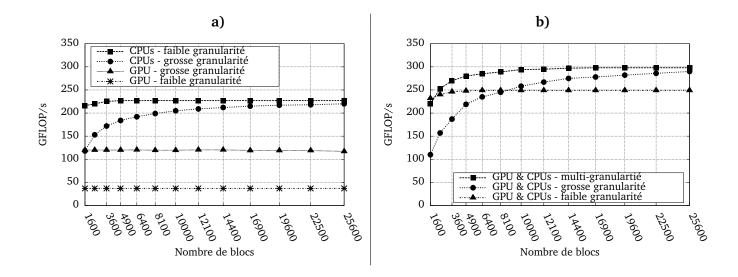

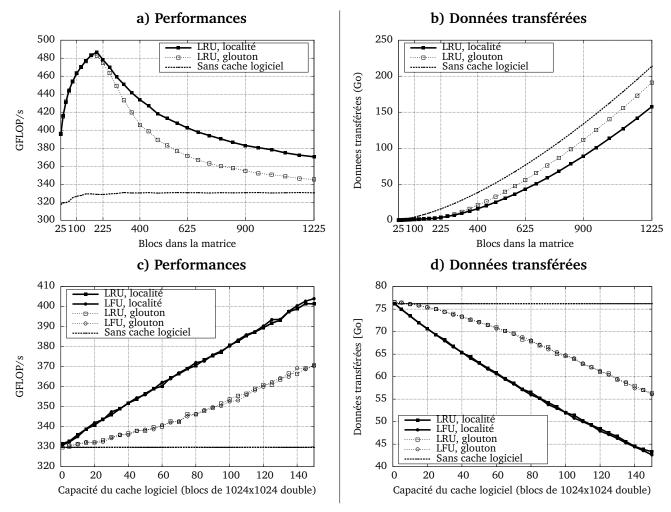

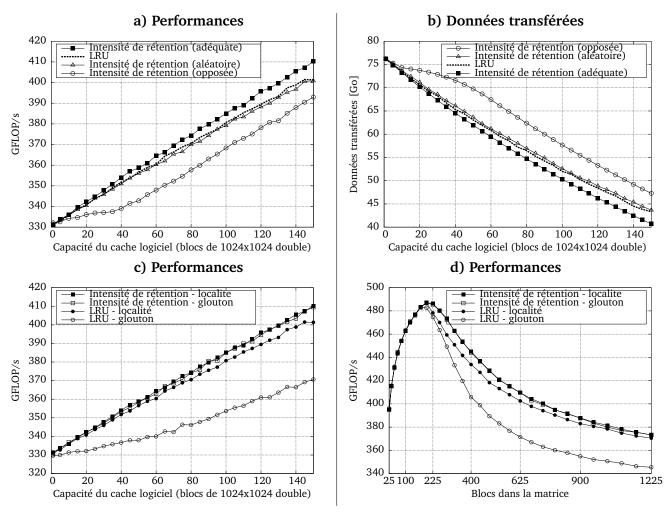

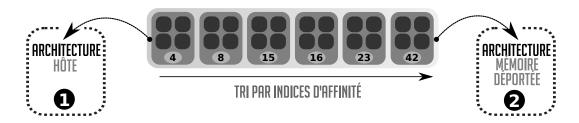

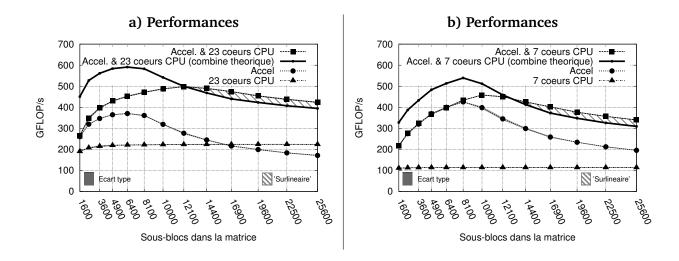

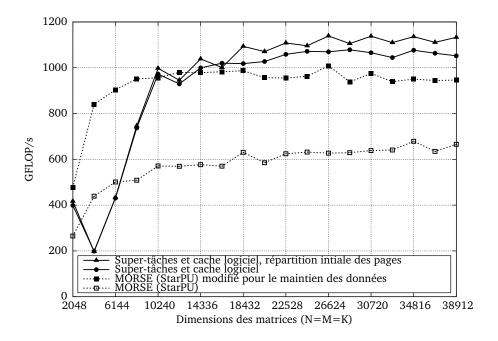

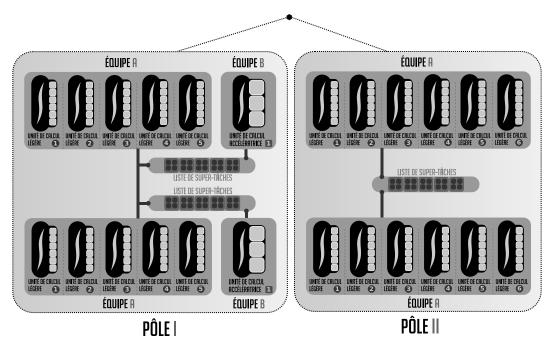

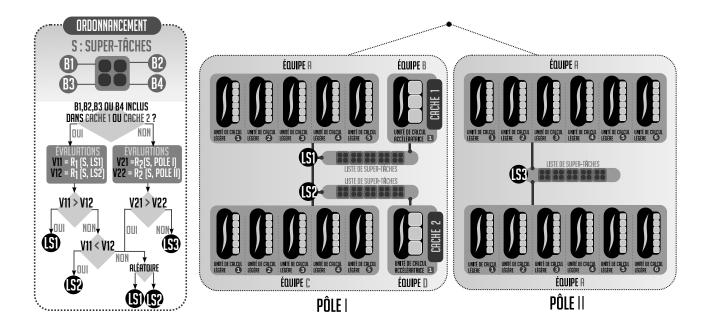

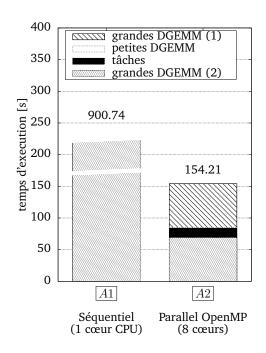

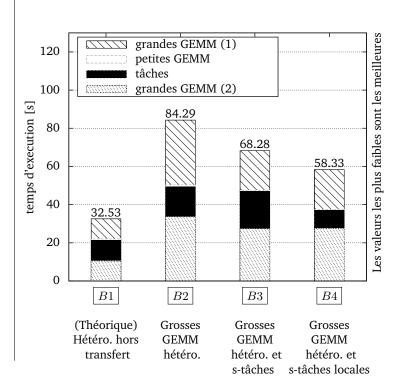

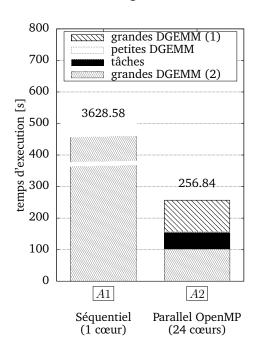

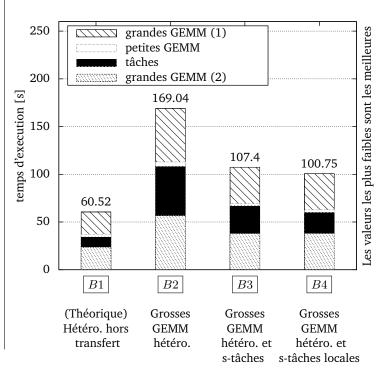

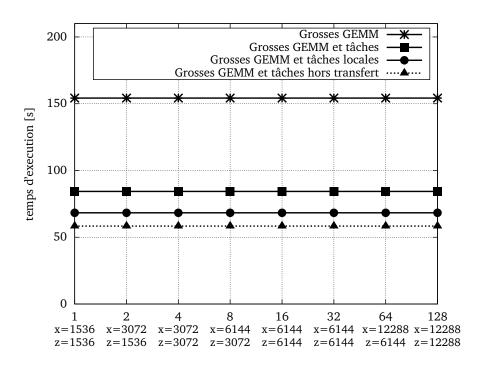

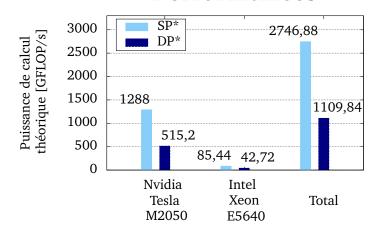

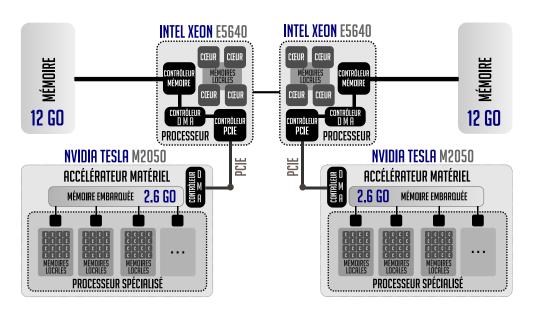

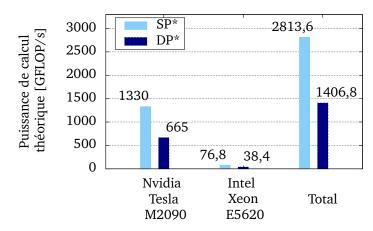

#### 1.4 Les supercalculateurs de prochaine génération